## Design Methodology for FPGA Implementation of Lattice Piecewise-Affine Functions

M. C. Martínez-Rodríguez<sup>2</sup>, I. Baturone<sup>1,2</sup>, P. Brox<sup>2</sup> Department of Electronics and Electromagnetism, University of Seville Microelectronics Institute of Seville (IMSE-CNM-CSIC) Seville, Spain December, 2011

## Design Methodology for FPGA Implementation of Lattice Piecewise-Affine Functions

- A piecewise-affine (PWA) function provides a linear (affine) output for each region in which the input domain, D, is partitioned.

- The lattice approach [1]

- allows the implementation of any continuous PWA function.

- selects the affine function without evaluating the boundaries.

- The algorithm extracts the lattice PWA representation using:

- a simplied structure matrix  $\rightarrow$  relation between regions

- A simplied parameter → affine regions

## Design Methodology for FPGA Implementation of Lattice Piecewise-Affine Functions

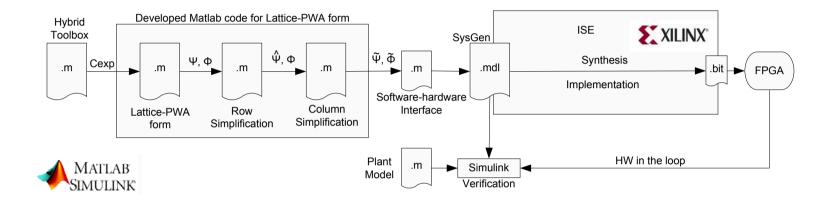

- The design methodology presented for FPGA implementation of continuous PWA functions based on lattice representation has been automated with Matlab&Simulink and ISE tools.

- The parameters required by the digital architecture are obtained from the algorithmic description of the problem.

- FPGA implementation results for applications in the control domain offer small size, high speed, and potentially no approximation error with regards to the optimum solution.