# Phase Transition Device for Phase Storing

María J. Avedillo, José María Quintana and Juan Núñez

*Abstract*— Nano-oscillators based on phase transitions materials (PTM) are being explored for the implementation of different non-conventional computing paradigms. This paper describes the capability of such autonomous non-linear oscillators to store phase-encoded information. A latch based in sub-harmonic injection locking using an oscillator composed of a PTM device and a transistor is described. Resistive coupling is used to inject both a required synchronization signal and the input to be stored. Operation of the proposed latch implementation, the embedding of functionality into the latch and its application to frequency division are illustrated and validated by simulation.

*Keywords*—Phase transition materials, VO<sub>2</sub>, Nanooscillators, Sub-Harmonic injection locking, Phase-encoded logic.

### INTRODUCTION

I.

Phase-Transition Materials (PTMs), with their abrupt switching between states with very different resistivity, are being explored both for implementing emerging devices, and for developing non-boolean computational paradigms.

Concerning the device application area, Phase-Change transistors (PCFETs) have been proposed by connecting a PTM to the source terminal of a FET. The abrupt insulatormetal transitions of the PTM are used as a mechanism to obtain steep switching and a boost in the  $I_{ON}/I_{OFF}$  [1], [2]. Several PCFETs exhibiting subtreshold slope (SS) under 60mV/dec have been experimentally obtained [3]-[5]. The combination of a PTM with Tunnel FETs (TFET) is also being explored to enhance the limited  $I_{ON}$  exhibited by TFETs [6]. In addition to reducing power consumption in conventional logic computation, associated with SS reduction [7], [8], recently, the mentioned PCFETs distinguishing features, such as improved  $I_{ON}$ - $I_{OFF}$  ratio and steep switching, are starting to be exploited to enhance specific circuit topologies [9], [10].

In addition, PTMs are considered as potential candidates to enable new computational paradigms such as neuromorphic architectures. In particular, different groups are exploiting the capability of a PTM device in series with a resistor to oscillate (under certain constraints on the resistor value [11]) in the implementation of coupled-oscillator based processing [12]-[17]. In many cases, VO<sub>2</sub> PTM devices are proposed to be used for their implementation. This paper shows a different application for the PTM-based oscillators in the context of Phase-encoded Logic (PeL).

PeL is an old idea [18] based on von Neumann's oscillatory computer. Instead of using voltage levels, logic values are encoded in the phase of an oscillating signal. This coding has

María J. Avedillo, José María Quintana and Juan Núñez are with the Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad of Sevilla). Av. Américo Vespucio 28, 41092, Sevilla, Spain. e-mail: {avedillo/josem/jnunez}@imse-cnm.csic.es. advantages in terms of noise immunity over level-logic coding for low voltage applications [19]. Key components of PeL logic are oscillators, which oscillating phase depends on the phases of the applied inputs. That is, the resulting phase is a logic function of the inputs. It was demonstrated that PeL can implement any logic functionality [20]. The lack of suitable on-chip oscillators limited their commercial application.

Recently, PeL has received renewed interest due to the opportunity that novel nanodevices offer for the compact and energy-efficient implementation of oscillators [21]. In particular, in [19], [22], a PeL latch based on Sub-Harmonic Injection Locking (SHIL) is proposed. They report the use of CMOS ring oscillators and demonstrates a sequential circuit but other oscillators can be used. In [21], many oscillators are evaluated as potential building blocks of oscillatory computing architectures. In terms of energy, relaxation oscillators based on PTMs exhibit good performance. They are reported to consume more than one order of magnitude less energy per cycle than ultra-low-power ring oscillators. They occupy the second position (together with spin-hall oscillators) in terms of energy efficiency, just after superconducting oscillators. In this simulation based paper, we show that the above-mentioned SHIL latch can be implemented with the PTM based oscillator and illustrates different functionalities build upon it.

This paper is organized as follows: Section II is devoted to the background on both the phase change based oscillator and the SHIL phenomena. Section III describes the operation of the proposed PTM based PeL Latch and results of electrical Spectre [23] simulations carried out are described and analyzed. Finally, key conclusions are provided in Section V.

# II. BACKGROUND

#### A. PTM based Oscillator

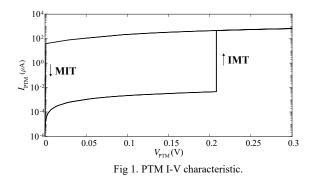

PTMs undergo insulator-metal transitions under given electrical stimuli. That is, they experience abrupt switching from/to a high resistivity state (insulating phase) to/from a low resistivity state (metallic phase). PTMs tend to stabilize in the insulating phase under no electrical stimuli. When the applied voltage increases and so the current density that flows through it reaches J<sub>C-IMT</sub>, Insulator to Metal Transition (IMT) occurs. Once in the metallic state, when the voltage decreases and so the current density reduces below J<sub>C-MIT</sub>, the Metal to Insulator Transition (MIT) takes place. Fig 1 shows the I-V characteristic of a PTM device. It corresponds to the PTM-Sim reported in [2], [7] with area  $A=42\cdot21nm^2$  and length L=40nm. It has been obtained with a Verilog-A model inspired by the macro-model proposed in [2]. Material properties of this device, as well as electrical parameters of its model, are depicted in Table I.  $V_{IMT}$  ( $V_{MIT}$ ) is the voltage at which the IMT (MIT) transition occurs. R<sub>INS</sub> (R<sub>MET</sub>) is the resistance of the PTM in the insulating (metallic) state. This is the PTM used in the work described in this paper. Since MIT and IMT transitions are abrupt but not instantaneous, a

Manuscript received May 14, 2019. Revised Sept. 10, 2019. This work has been funded by Ministerio de Economía y Competitividad del Gobierno de España with support from FEDER (Project TEC2017-87052-P).

TABLE I. PHYSICAL AND ELECTRICAL PARAMETERS OF THE SIMULATED

| PTM DEVICE.         |                       |                  |                       |  |

|---------------------|-----------------------|------------------|-----------------------|--|

| Physical parameters |                       | Electr           | Electrical parameters |  |

| $\rho_{INS}$        | 100Ω·cm               | R <sub>INS</sub> | 45.2MΩ                |  |

| $\rho_{\text{MET}}$ | 0.001Ω·cm             | R <sub>MET</sub> | 452Ω                  |  |

| J <sub>C-MIT</sub>  | 8000A/cm <sup>2</sup> | V <sub>MIT</sub> | 32µV                  |  |

| J <sub>C-IMT</sub>  | 520A/cm <sup>2</sup>  | V <sub>IMT</sub> | 204mV                 |  |

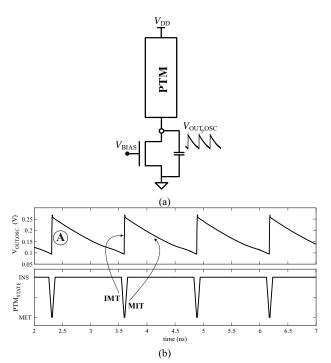

Fig 2. HyperFET oscillator a) topology, b) operation waveforms.

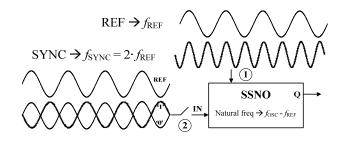

Fig 3. Sub-harmonic injection locking (SHIL) latch (after [19]).

transition time (TT) is also considered. The value reported in [2] (50ps) has been used. Also, a parallel parasitic capacitance of 1fF has been also included, according to [2]. Fig 2a shows a PTM based oscillator [11], [13]. The predictive transistor model of an HP 14nm transistor [25], [26] is used. This transistor has been selected because it is the

one used in combination with the PTM-Sim in [2]. The circuit oscillates for a range of VBIAS values. Fig 2b depicts simulated waveforms for the oscillator output,  $V_{OUT,OSC}$  with  $V_{DD}$  = 0.3V and  $V_{BIAS}$  = 0.14V. Transistor gate width (length) has been set to 1.12µm (18nm). The state of the PTM is also shown in order to better illustrate the circuit behavior. PTM<sub>STATE</sub>='INS' means the device is in the insulating state. PTM<sub>STATE</sub>='MET' corresponds to the device in the metallic state. Assuming the PTM is in an insulating state (point "A" in Fig 2b), the oscillator output is discharged through the transistor. This increases the voltage drop across the PTM (V<sub>DD</sub> - V<sub>OUT,OSC</sub>) and so current through it increases. Once enough current density circulates (J<sub>C-IMT</sub>), it switches to the metallic state. Equivalently, using the electrical model, the switching to the metallic state occurs once the PTM voltage reaches  $V_{IMT}$ . The output is then charged through the PTM. This charging is very fast because of the low R<sub>MET</sub> value and reduces the voltage seen by the PTM until it reaches V<sub>MIT</sub> and the metallic to insulating state transition occurs. Note the frequency of the signal can be controlled with voltage  $V_{BIAS}$ . PTM based oscillators using VO<sub>2</sub> have been experimentally shown and are being explored to implement novel computational paradigms as it was already stated in the introductory section.

### B. SHIL latch

Fig 3 depicts the sub-harmonic injection locking based latch for phase-encoded information. It is composed of a selfsustainable (autonomous) non-linear oscillator (SSNO), which produce periodic signals without any external frequency reference. When a suitable synchronization signal (SYNC) is injected into the oscillator (1), SHIL occurs and the oscillator adopts a frequency half the frequency of SYNC ( $f_{SYNC}$ ) and becomes phase synchronized within one of two possible phases that are 180° apart. For this to occur, the natural frequency of the oscillator must be close to  $f_{SYNC}/2$ . In order to be able to distinguish the two SHIL phases, a REF signal of frequency  $f_{SYNC}/2$  and phase-synchronized with SYNC is assumed to be available. The SHIL state in phase with REF represents one of the two logic values and the other one (180° apart) the other value.

The phase can be controlled by injecting a phase-encoded signal, IN (2). The oscillator adopts the phase of IN (logic value) and retains it when IN is no longer applied.

SSNOs (and so SHIL latches) can be built from different material system exploiting distinct physics phenomena. Examples are CMOS ring oscillators, MEMS/NEMS-based oscillators, spin-torque nano-oscillators or mechanical metronomes [24]. In this paper, we show that also PTM based oscillators can be used to implement this phase-encoded latch.

In addition, the SHIL operation of PTM based oscillators demonstrated in this paper could potentially increase robustness of the widely explored coupled oscillators processing architectures mentioned in the introductory section [27].

# SHIL HYPERFET LATCH

III.

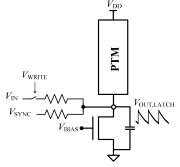

The PTM oscillator described in Part A of Section II has been used to build the SHIL latch in Part B. Fig 4 depicts its schematic. Note that resistive coupling is used to inject the synchronization signal  $V_{SYNC}$ . Phase-encoded input to be

Fig 4. Schematic of the proposed SHIL latch.

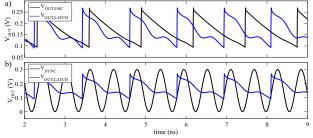

Fig 5. Simulation results for an oscillator with  $V_{SYNC}$  injected. a) Comparison of autonomous oscillator output ( $V_{OUT,OSC}$ ) and with  $V_{SYNC}$ injected ( $V_{OUT,LATCH}$ ), b)  $V_{OUT,LATCHH}$  and  $V_{SYNC}$ .

stored  $(V_{IN})$  is also applied through a resistance under the control of signal  $V_{WRITE}$ .

Let us first show the effect of applying  $V_{SYNC}$ . For that, Fig 5a compares simulation results obtained with Spectre for the autonomous oscillator in Fig 2 ( $V_{OUT,OSC}$ ) and for the latch ( $V_{OUT,LATCH}$ ) with  $V_{SYNC}$  injected, with an input resistance of 80k $\Omega$ , and no input applied ( $V_{WRITE} = 0$ ). Note their frequencies are different. As it can be observed in Fig 5b, the latch locks with  $V_{SYNC}$  and exhibits a frequency that is half of the  $V_{SYNC}$  one. That is, it oscillates with  $V_{REF}$  frequency as explained in the previous section. In addition, two phases (180° apart) with respect to  $V_{REF}$  are possible for  $V_{OUT,LATCH}$ . This can be exploited to implement a latch storing phase-encoded information by shortly applying  $V_{IN}$  to control the stored phase, as we explain below.

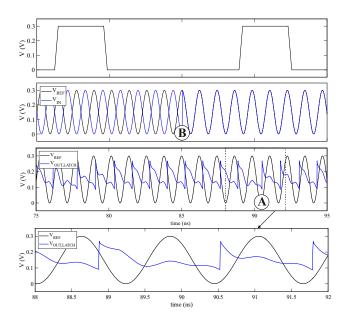

Fig 6 depicts the operation of the latch. Input resistance has been set to  $90k\Omega$ . Waveforms for  $V_{WRITE}$ ,  $V_{IN}$  and  $V_{OUT,LATCH}$ are shown. To ease analysis,  $V_{REF}$  is shown overlapped with both  $V_{IN}$  and  $V_{OUT,LATCH}$ , so that phase information of each signal can be identified. The experiment shown corresponds to first storing  $V_{REF}$  shifted by 180° ( $\overline{V}_{REF}$ ) with the first V<sub>WRITE</sub> pulse shown and then applying V<sub>REF</sub> (second V<sub>WRITE</sub> pulse). Each input is applied for a few periods of the V<sub>SYNC</sub> signal. That is, the switch is closed ( $V_{WRITE} = '1'$ ) for a few periods to store the input information. Correct operation has been obtained if the switch is closed for just one V<sub>SYNC</sub> period. Note there are two phase-locking states between VREF and VOUTLATCH as we have anticipated. Correct behavior is observed. The phase is stored when V<sub>WRITE</sub> is activated (for example "A" in the figure) while it is kept if  $V_{IN}$  phase changes with  $V_{WRITE}$  = '0'. For example, point "B" in the figure in which it is shown that the input phase changes but the output latch phase doesn't. Waveforms at the bottom of the figure depict the transition region from one stored phase to another.  $V_{REF}$  ( $\overline{V_{REF}}$ ) is stored as  $V_{OUT,LATCH}$  with its maximum value before (after) the closest maximum  $V_{\text{REF}}$ value.

In order to further illustrate the latch operation, we have alternatively applied  $V_{REF}$  and  $\overline{V_{REF}}$ , and the phase difference

Fig 6. Operation of SHIL latch. Waveforms.

Fig 7. Operation of SHIL latch. Phase difference.

between  $V_{REF}$  and  $V_{OUT,LATCH}$  has been measured (Fig 7). Reference points for such measurement are the maximum of each signal. Stable 180° apart phase-difference values are obtained when no input is applied. These values are different form 0° and 180° because of the non-sinusoidal latch output and the selected measurement criteria. However, the different sign obtained for both possible phases eases the analysis of the results. A negative (positive) value is associated with the storing of  $V_{REF}$  ( $\overline{V_{REF}}$ ). During transitions, other phasedifferences occur.

It is relevant exploring operation of the proposed latches under PTM parameter variations because they affect oscillator frequency and it is well known that natural operating frequency of intrinsic oscillator needs to be close enough to V<sub>REF</sub> frequency for SHIL phenomenon to occur [22]. We have determined a correct behavior of our design of the proposed SHIL latch for V<sub>IMT</sub>  $\pm$  5%. This robustness is similar to reported results of other applications using PTM based oscillators [14]. We have checked that the allowed range for natural frequencies can be optimized by adjusting the values of the coupling resistors, although an exhaustive optimization has not been carried out.

### IV. CIRCUITS WITH THE SHIL HYPERFET LATCH

A number of circuits using the SHIL latch described in the previous section are illustrated.

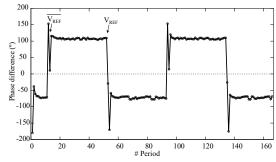

First, it is shown that majority functionality can be easily added to the proposed latch. Fig 8a shows the truth table of a

Fig 8. SHIL three-input majority latch. (a) Truth table (b) Schematic. (v) Waveforms. (d) Phase difference.

three-input majority function and Fig 8b depicts the schematic of a three-input majority latch. This circuit stores the majority phase of its three inputs. For example, for ( $V_{IN1}$ ,  $V_{IN2}$ ,  $V_{IN3}$ ) = ( $\overline{V_{REF}}$ ,  $\overline{V_{REF}}$ ,  $V_{REF}$ ), the phase corresponding to  $\overline{V_{REF}}$  is stored and for ( $V_{IN1}$ ,  $V_{IN2}$ ,  $V_{IN3}$ ) = ( $\overline{V_{REF}}$ ,  $\overline{V_{REF}}$ ,  $V_{REF}$ ), the phase corresponding to  $V_{REF}$  is stored. Fig 8c depicts simulation results for those input combinations. Fig 8d shows phase difference (similar to Fig 7) for the eight input combinations. 0° (180°) means that  $V_{REF}$  ( $\overline{V_{REF}}$ ) is applied and  $V_{WRITE}$  is also displayed. It can be beerved that, again, two 180° apart phase states are stored into the latch. That stored information changes only when  $V_{WRITE}$  is activated and according to the applied input combination. A correct operation for all inputs combinations has been obtained.

It is interesting to realize that the boolean CMOS implementation functionally equivalent to this circuit requires seven NAND gates plus one inverter.

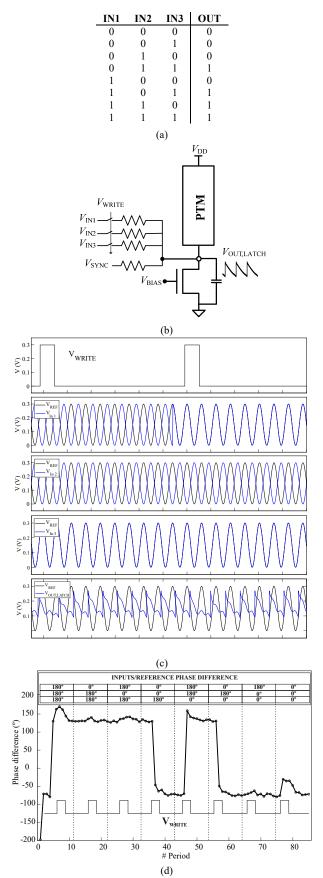

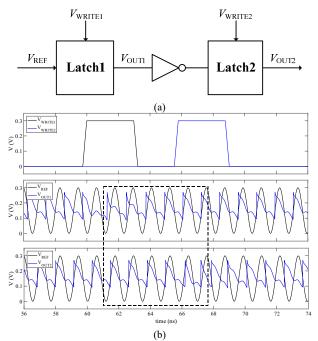

Second, the operation of a circuit in which several SHIL latches are chained is depicted. Clearly it is not possible to directly connect the output of a SHIL latch to the input of another because both of them would interact, and there is no guarantee that the first one forces the phase of the second. However it is possible to build logic circuits if somehow one oscillator is isolated from the other. For that a CMOS inverter (or a pair of them) can be used. Fig 9a shows the concatenation of two latches using an inverter between them. That is the inversion of the stored signal in Latch<sub>1</sub> is used as input for Latch<sub>2</sub>. Fig 9b depicts simulated waveforms using non-overlapped write signals, as it is typical of latch based circuits. The output of each of the two latches (V<sub>OUT1</sub> and V<sub>OUT2</sub>) overlapped with V<sub>REF</sub> are shown. It can be observed that initially (before the V<sub>WRITE1</sub> pulse), the latches store different values (complementary). With the V<sub>WRITE1</sub> pulse, the content of Latch1 is changed and now both latches store same value (marked in the figure with a rectangle). With the V<sub>WRITE2</sub> pulse the "complement" of the Latch<sub>1</sub> is stored in Latch<sub>2</sub>. After, the latches store complementary values again. It is well known that the majority logic function and NOT form a complete logic system. This means any combinational logic function can be implemented with them. We have shown in previous experiment hat the HyperFET SHIL latch can implement the majority and that the NOT for phaseencoded signals can be implemented with an inverter. In adittion we can connect gates. Thus, any logic circuit could be implemented with the described SHIL building blocks. Finally, a different application of the SHIL HyperFET latch

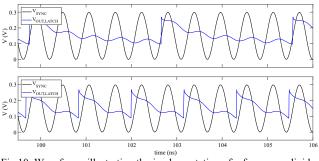

is illustrated. The behavior of this block applying only the synchronization signal ( $V_{SYNC}$ ) can be described as dividing the frequency of  $V_{SYNC}$  by 2. Division by another factor (N) can be also achieved by applying a  $V_{SYNC}$  signal of frequency close to N times the natural frequency of the autonomous oscillator. Alternatively, since the natural frequency of the oscillator can be controlled by the voltage applied to the gate of the transistor, the division factor could be tuned. Fig 10 depicts the output of the latch for different gate voltages. Top waveform ( $V_{BIAS}$ =110mV) corresponds to division by 5 and bottom waveform ( $V_{BIAS}$ =140mV) to division by 2.

Fig 9. Interconnection of two SHIL latches using a CMOS inverter to isolate them. (a) Schematic (b) Simulated waveforms.

Fig 10. Waveforms illustrating the implementation of a frequency divider from a SHIL HyperFET latch. The upper figure corresponds to a division by 5 and the lower figure by 2.

# V. CONCLUSIONS

It has been shown that a PTM based oscillator can be used to store phase-encoded information. For that, sub-harmonic injection locking is exploited. Up to our knowledge, it is the first work showing SHIL with PTM based oscillators. In addition to memory, majority and NOT functionality, that conforms a complete logic set, have been shown. A compact, energy efficient nano-oscillator has been identified as a potential candidate to implement phase encoded logical, although further work is required to evaluate it. Additionally, the showed SIHL operation of PTM based oscillators can have application in neuromorphic networks based on coupled VO2 networks.

#### References

- [1] N. Shukla A. V. Thathachary, A. Agrawal, H. Paik, A. Aziz, D. G. Schlom, S.K. Gupta, R. Engel-Herbert, and S. Datta, "A steep-slope transistor based on abrupt electronic phase-transition," *Nature Commun.*, vol. 6, pp. 7812-1–7812-6, 2015. DOI: https://doi.org/10.1038/ncomms8812.

- [2] A. Aziz, N. Shukla, S. Datta and S. K. Gupta., "Steep Switching Hybrid Phase Transition FETs (Hyper-FET) for Low Power Applications: A Device-Circuit Co-design Perspective–Part I," in *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 1350-1357, March 2017. doi: 10.1109/TED.2016.2642884.

- [3] J. Frougier, N. Shukla, D. Deng, M. Jerry, A. Aziz, L. Liu, G. Lavallee,

T. S. Mayer, S. Gupta and S. Datta, "Phase-transition-FET Exhibiting Steep Switching Slope of 8mV/decade and 36% Enhanced ON Current", in 2016 IEEE Symposium on VLSI Technology. DOI: 10.1109/VLSIT.2016.7573445.

- [4] J. Song, J. Woo, S. Lee, A. Prakash, J. Yoo, K. Moon, and H. Hwang, "Steep Slope Field-Effect Transistors With Ag/TiO<sub>2</sub>-Based Threshold Switching Device," in *IEEE Electron Device Letters*, vol. 37, no. 7, pp. 932-934, July 2016. Doi:10.1109/LED.2016.2566661.

- [5] A. Verma, B. Song, D. Meyer, B. Downey, V. Wheeler, H. Xing and D. Jena, "Demonstration of GaN PCFETs with ALD V<sub>02</sub>," 2016 74th Annual Device Research Conference (DRC), Newark, DE, 2016, pp. 1-2. DOI: 10.1109/DRC.2016.7548397.

- [6] W. A. Vitale, E. A. Casu, A. Biswas, T. Rosca, C. Alper, A. Krammer, G. V. Luong, Q. T. Zhao, S. Mantl, A. Schüler, and A. M. Ionescu, "A Steep-Slope Transistor Combining Phase-Change and Band-to-Band-Tunneling to Achieve a sub-Unity Body Factor," *Nature Scientific Reports*, vol. 7, Article number: 355, Mar. 2017. DOI: https://doi.org/10.1038/s41598-017-00359-6.

- [7] A. Aziz, N. Shukla, S. Datta and S. K. Gupta., "Steep Switching Hybrid Phase Transition FETs (Hyper-FET) for Low Power Applications: A Device-Circuit Co-design Perspective–Part II," in *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 1358-1365, March 2017. doi: 10.1109/TED.2017.2650598.

- [8] M. J. Avedillo and J. Núñez. "Insights into the Operation of Hyper-FET based Circuits", *IEEE Transactions on Electron Devices*. vol. 64, no. 9, pp. 3912-3918, Sept. 2017. doi: 10.1109/TED.2017.2726765.

- [9] A. Aziz, X. Li, N. Shukla, S. Datta, M.-F. Chang, V. Narayanan and S. K. Gupta. "Low Power Current Sense Amplifier Based on Phase Transition Material", 2017 75th Annual Device Research Conference (DRC), South Bend, IN, 2017, pp. 1-2. DOI: 10.1109/DRC.2017.7999425.

- [10] M. J. Avedillo, M. Jiménez and J. Núñez, "Phase Transition FETs for Improved Dynamic Logic Gates," in *IEEE Electron Device Letters*, vol. 39, no. 11, pp. 1776-1779, Nov. 2018. doi: 10.1109/LED.2018.2871855

- [11] P. Maffezzoni, L. Daniel, N. Shukla, S. Datta, and A. Raychowdhury, "Modeling and Simulation of Vanadium Dioxide Relaxation Oscillators", *IEEE Transactions On Circuits And Systems—I*, Vol. 62, pp. 2207-2215, Sep. 2015.

- [12] A.A. Sharma, J.A, Bain, and J.A. Weldon, "Phase Coupling and Control of Oxide-Based Oscillators for Neuromorphic Computing," *IEEE Journal of Exploratory Solid-State Computational Devices and Circuits*, Vol 1, pp. 58-66, 2015.

- [13] W. Y. Tsai, X. Li, M. Jerry, B. Xie, N. Shukla, H- Liu, at al., "Enabling New Computation Paradigms with HyperFET - An Emerging Device," in *IEEE Transactions on Multi-Scale Computing Systems*, vol. 2, no. 1, pp. 30-48, Jan.-March 1 2016. doi: 10.1109/TMSCS.2016.2519022.

- [14] E. Corti, B. Gotsmann, K. Moselund, I. Stolichnov, A. Ionescu, S. Karg, "Resistive coupled VO2 oscilators for image recognition", 2018 IEEE International Conference on Rebooting Computing (ICRC), McLean, VA, USA, 2018, pp. 1-7. DOI: 10.1109/ICRC.2018.8638626

- [15] A. Parihar, N. Shukla, M. Jerry, S. Datta and A. Raychowdhury, "Vertex coloring of graphs via phase dynamics of coupled oscillatory networks", *Nature Scientific Reports*. vol. 7, no. 911. April 2018. DOI:10.1038/s41598-017-00825-1.

- [16] Velichko, M. Belyaev and P. Boriskov, "A model of an Oscillatory Neural Network with Multilevel Neurons for Pattern Recognition and Computing", *Electronics*, vol. 8, no. 75, Jan. 2019, DOI: 10.3390/electronics8010075.

- [17] A. Raychowdhury, A. Parihar, G. H. Smith, V. Narayanan, G. Csaba, M. Jerry, Wolfgang Porod and S. Datta," Computing With Networks of Oscillatory Dynamical Systems", *Proceedings of the IEEE*, vol. 107, no. 1, pp. 73-89, Jan. 2019

- [18] E. Goto, "The parametron, a digital computing element which utilizes parametric oscillation," *Proc. of the IRE.*, vol. 47, nº 8, p. 1304–1316, 1959.

- [19] J. Roychowdhury, "Boolean Computation Using Self-Sustaining Nonlinear Oscillators," *Proceedings of the IEEE*, vol. 103, nº 11, pp. 1958 - 1969, 2015.

- [20] S. Muroga, T. Takashima, "The parametron digital computer Musasino-I", *IRE Transaction on Electronics Computers*, pp. 308-316, Sep. 1959.

- [21] G. Csaba, W. Porod, "Perspective of Using Oscillators for Computing and Signal Processing", http://adsabs.harvard.edu/abs/2018arXiv180509056C, 2018.

- [22] T. Wang and J. Roychowdhury, "PHLOGON: PHase-based LOgic using oscillatory nansystems," de Unconventional Computation and Natural Computation, Berlin, Springer-Verlag, 2014, pp. 353-366.

- [23] Spectre circuit simulator. https://www.cadence.com/content/cadencewww/global/en\_US/home/tools/custom-ic-analog-rf-design/circuit-

simulation/spectre-circuit-simulator.html.

- [24] Wang, Tianshi. "Achieving Phase-based Logic Bit Storage in Mechanical Metronomes". arXiv:1710.01056 [cs]. Oct. 2017.

- [25] W. Zhao and Y. Cao, "New generation of predictive technology model for sub-45nm design exploration," in Proc. 7th Int. Symp. Quality Electron. Des., Mar. 2006, pp. 585–590. DOI: 10.1109/ISQED.2006.9.

- [26] Predictive Technology Model website. <u>http://ptm.asu.edu</u>.

- [27] G. Csaba, T. Ytterdal and W. Porod, "Neural network based on parametrically-pumped oscillators," 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, 2016, pp. 45-48. doi: 10.1109/ICECS.2016.7841128