Departament d'Enginyeria Electrònica

### Low-Power CMOS Digital-Pixel Imagers for High-Speed Uncooled PbSe IR Applications

Josep Maria Margarit Taulé

A dissertation submitted for the degree of

Doctor of Philosophy by the Universitat Politècnica de Catalunya,

under the PhD program in ELECTRONIC ENGINEERING

November 2015

Revised

Dr. Francesc Serra Graells, Associate Professor at the Microelectronics and Electronic Systems Department of Universitat Autònoma de Barcelona, Dr. Lluís Terés Terés, Tenured Scientist at Consejo Superior de Investigaciones Científicas, and Dr. Jordi Madrenas Boadas, Associate Professor at the Electronic Engineering Department of Universitat Politècnica de Catalunya,

that the dissertation "Low-Power CMOS Digital-Pixel Imagers for High-Speed Uncooled PbSe IR Applications" presented by Josep Maria Margarit Taulé in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electronic Engineering has been performed under their supervision at the Institute of Microelectronics of Barcelona belonging to the *Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas*, and has been tutored at the Electronic Engineering Department of *Universitat Politècnica de Catalunya*.

| Supervisors | Dr. Francesc Serra Graells |  |

|-------------|----------------------------|--|

|             | Dr. Lluís Terés Terés      |  |

| Tutor       | Dr. Jordi Madrenas Boadas  |  |

|             |                            |  |

.....

In the loving memory of my brother, Pere, and my grandparents Eulalia and Josep.

## Abstract

This PhD dissertation describes the research and development of a new lowcost medium wavelength infrared (MWIR) monolithic imager technology for high-speed uncooled industrial applications. It takes the baton on the latest technological advances in the field of vapour phase deposition (VPD) PbSe-based MWIR detection accomplished by the industrial partner NIT S.L., adding fundamental knowledge on the investigation of novel VLSI analog and mixed-signal design techniques at circuit and system levels for the development of the readout integrated device attached to the detector.

The work supports on the hypothesis that, by the use of the preceding design techniques, current standard inexpensive CMOS technologies fulfill all operational requirements of the VPD PbSe detector in terms of connectivity, reliability, functionality and scalability to integrate the device. The resulting monolithic PbSe-CMOS camera must consume very low power, operate at kHz frequencies, exhibit good uniformity and fit the CMOS read-out active pixels in the compact pitch of the focal plane, all while addressing the particular characteristics of the MWIR detector: high dark-to-signal ratios, large input parasitic capacitance values and remarkable mismatching in PbSe integration.

In order to achieve these demands, this thesis proposes null inter-pixel crosstalk vision sensor architectures based on a digital-only focal plane array (FPA) of configurable pixel sensors. Each digital pixel sensor (DPS) cell is equipped with fast communication modules, self-biasing, offset cancellation, analog-to-digital converter (ADC) and fixed pattern noise (FPN) correction. In-pixel power consumption is minimized by the use of comprehensive MOSFET subthreshold operation.

The main aim is to potentiate the integration of PbSe-based infrared (IR)image sensing technologies so as to widen its use, not only in distinct scenarios, but also at different stages of PbSe-CMOS integration maturity. For this purpose, we posit to investigate a comprehensive set of functional blocks distributed in two parallel approaches:

- Frame-based "Smart" MWIR imaging based on new DPS circuit topologies with gain and offset FPN correction capabilities. This research line exploits the detector pitch to offer fully-digital programmability at pixel level and complete functionality with input parasitic capacitance compensation and internal frame memory.

- Frame-free "Compact"-pitch MWIR vision based on a novel DPS lossless analog integrator and configurable temporal difference, combined with asynchronous communication protocols inside the focal plane. This strategy is conceived to allow extensive pitch compaction and readout speed increase by the suppression of in-pixel digital filtering, and the use of dynamic bandwidth allocation in each pixel of the FPA.

In order to make the electrical validation of first prototypes independent of the expensive PbSe deposition processes at wafer level, investigation is extended as well to the development of affordable sensor emulation strategies and integrated test platforms specifically oriented to image read-out integrated circuits. DPS cells, imagers and test chips have been fabricated and characterized in standard  $0.15\mu$ m 1P6M,  $0.35\mu$ m 2P4M and  $2.5\mu$ m 2P1M CMOS technologies, all as part of research projects with industrial partnership.

The research has led to the first high-speed uncooled frame-based IR quantum imager monolithically fabricated in a standard VLSI CMOS technology, and has given rise to the Tachyon series [1], a new line of commercial IR cameras used in real-time industrial, environmental and transportation control systems. The frame-free architectures investigated in this work represent a firm step forward to push further pixel pitch and system bandwidth up to the limits imposed by the evolving PbSe detector in future generations of the device.

## Acknowledgements

My first and foremost acknowledgments to **Paco Serra** and **Lluís Terés** for their incombustible guidance, moving enthusiasm and great patience. Thanks for believing in my work from the start to the very end, and giving me the opportunity to grow as a scientist and as a person in the IMB.

My next big thank you to the NIT people, **Carlos Fernández, Luis Gómez, Raúl Gutiérrez, Maria Teresa Montojo, Germán Vergara** and **Víctor Villamayor**. Your immediate feedback, exhaustive characterization and methodical debugging were invaluable throughout this work.

I am also grateful to all the previous, the current and the almost members of the ICAS team that helped me along this dissertation. Thanks to Xavier Bullich, Álvaro Calleja, Adrià Conde, Michele Dei, Roger Durà, Roger Figueras, Aymen Jemni, Ricardo Martínez, Andreu Marzal, Sergio Morlans, Jofre Pallarès, Xavier Redondo, Justo Sabadell, Jordi Sacristán, Stepan Sutula, Fortià Vila, Francesc Vila and Pedro Zuccarello, for the bright discussions, helpful suggestions and support. Thanks to Josep Lorente and Joan Puertas for their crash course in PCB design, and to Enric Cabruja and Alberto Moreno for making possible the flip-chip and the wire-bonding of the ICs. To Albert Beltran, Sergi Peña and Jared Villanueva my gratitude for their major, hard-working contributions to Matlab simulations, pixel design, and test, respectively. My appreciation also to **Jordi Madrenas** for his neat academic supervision as tutor at the UPC.

To **Tobi Delbruck** and **Shih-Chii Liu**, thanks for giving me the opportunity to visit the INI and to come back as a postdoc. I was immediately captivated by the warm and stimulating atmosphere of the Institute, and the humility and talent of its people. But amongst all, I learned A LOT. I am sure that was only the beginning of many fruitful collaborations between both centers. Thanks to **Raphael Berner** as well for his conclusive advice in the design of AER interfaces, and to **Mathias Bannwart**, for his master lessons on german, cooking, and friendship.

Gràcies a la familia i als amics! A la meva mare i la meva germana, les dues Roses, i a l'Andreu, el Dani, l'Ivan, la Neus, l'Oscar i el Xavi per les incontables paraules de suport, ànims i mostres d'afecte que m'heu regalat. I gràcies als meus nebots Carla, Roger i Pau per robar-me sempre un somriure.

Because I would not have succeeded without your intellectual and emotional support, there is a bit of every one of you in this thesis.

#### THANK YOU!!

# Contents

| 1 | Intr | oductio | on                                 | 1  |

|---|------|---------|------------------------------------|----|

|   | 1.1  | Seeing  | Beyond the Visible                 | 1  |

|   |      | 1.1.1   | Vision Cameras                     | 1  |

|   |      | 1.1.2   | Seizing the Red End                | 3  |

|   | 1.2  | Commo   | on Metrics and Figures of Merit    | 7  |

|   | 1.3  | IR Dire | ect Detectors                      | 12 |

|   |      | 1.3.1   | Thermal and Photonic Transduction  | 12 |

|   |      | 1.3.2   | IR Detection Today                 | 14 |

|   | 1.4  | Uncool  | ed PbSe Photoconductive Technology | 16 |

|   |      | 1.4.1   | Detection Basis                    | 16 |

|   |      | 1.4.2   | Device Performance                 | 19 |

|   |      | 1.4.3   | Electrical Model                   | 22 |

|   | 1.5  | CMOS    | IR Imagers                         | 24 |

|          |     | 1.5.1  | Readout Techniques                                                                  |

|----------|-----|--------|-------------------------------------------------------------------------------------|

|          |     | 1.5.2  | FPA Architectures                                                                   |

|          |     | 1.5.3  | State-of-the-Art IR Vision Sensors                                                  |

|          | 1.6 | Objec  | tives and Scope $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 31$ |

|          |     | 1.6.1  | Motivation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 31$      |

|          |     | 1.6.2  | R&D Context                                                                         |

|          |     | 1.6.3  | Working Hypothesis                                                                  |

|          |     | 1.6.4  | The Challenges                                                                      |

|          |     | 1.6.5  | Methodology and Contents                                                            |

| <b>2</b> | Fra | me-Ba  | sed Smart IR Imagers 43                                                             |

|          | 2.1 | Image  | r Architecture and Operation Proposal 43                                            |

|          | 2.2 | All-Di | gital Program-In and Read-Out Interface 47                                          |

|          |     | 2.2.1  | Motivation and Design Proposal                                                      |

|          |     | 2.2.2  | Compact CMOS Implementation                                                         |

|          | 2.3 | Input  | Signal Conditioning                                                                 |

|          |     | 2.3.1  | Motivation and Design Proposal                                                      |

|          |     | 2.3.2  | Compact CMOS Implementation                                                         |

|          | 2.4 | Async  | hronous ADC with CDS                                                                |

|          |     | 2.4.1  | Motivation and Design Proposal 63                                                   |

|          |     | 2.4.2  | Compact CMOS Implementation 67                                                      |

|          | 2.5 | Indivi | dual Gain Tuning                                                                    |

|          |     | 2.5.1  | Motivation and Design Proposal                                                      |

|          |     | 2.5.2  | Compact CMOS Implementation                                                         |

|          | 2.6 | Local  | Bias Generation                                                                     |

|   |      | 2.6.1   | Motivation and Design Proposal                                       | 80 |

|---|------|---------|----------------------------------------------------------------------|----|

|   |      | 2.6.2   | Compact CMOS Implementation                                          | 82 |

| 3 | Fra  | me-Fre  | ee Compact-Pitch IR Imagers                                          | 85 |

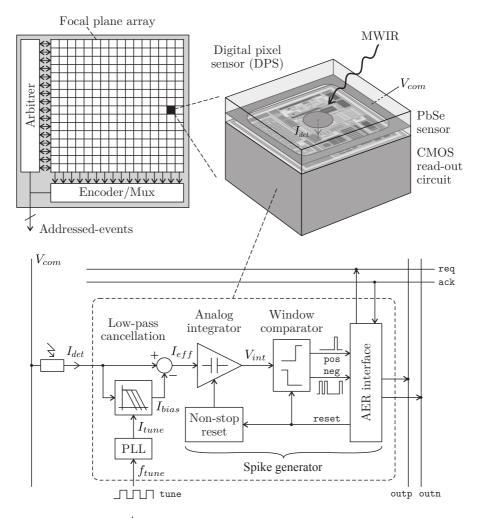

|   | 3.1  | Image   | r Architecture and Operation Proposal                                | 85 |

|   | 3.2  | Event-  | Driven Communications                                                | 86 |

|   |      | 3.2.1   | Motivation and Design Proposal                                       | 86 |

|   |      | 3.2.2   | In-pixel compact CMOS Implementation                                 | 92 |

|   | 3.3  | Self-B  | iasing and Temporal-Difference Filtering                             | 95 |

|   |      | 3.3.1   | Motivation and Design Proposal                                       | 95 |

|   |      | 3.3.2   | Compact CMOS Implementation                                          | 97 |

|   | 3.4  | Digita  | l Contrast Tuning                                                    | 03 |

|   |      | 3.4.1   | Motivation and Design Proposal                                       | 03 |

|   |      | 3.4.2   | Compact CMOS Implementation                                          | 04 |

|   | 3.5  | Reset-  | Insensitive Spike-Counting ADC                                       | 06 |

|   |      | 3.5.1   | Motivation and Design Proposal                                       | 06 |

|   |      | 3.5.2   | Compact CMOS Implementation                                          | 11 |

|   | 3.6  | Fair A  | E Arbitration                                                        | 13 |

|   |      | 3.6.1   | Motivation and Design Proposal                                       | 13 |

|   |      | 3.6.2   | Compact CMOS Implementation                                          | 15 |

| 4 | Pixe | el Test | Chips in $0.35 \mu m$ and $0.15 \mu m$ CMOS Technologies 11          | 19 |

|   | 4.1  | ,       | um-Pitch Smart Pixel with Offset Auto-Calibration and<br>Programming | 20 |

|   |      | 4.1.1   | Full-Custom ASIC Design                                              | 22 |

|   |      |         |                                                                      |    |

|   |      | 4.1.2            | Experimental Results                                                                                                                                                              | 127 |

|---|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.2  | A 200            | $\mu m$ and 130 $\mu m$ -pitch Smart Pixel with Full Programma-                                                                                                                   |     |

|   |      | bility           |                                                                                                                                                                                   | 137 |

|   |      | 4.2.1            | Full-Custom ASIC Designs                                                                                                                                                          | 139 |

|   |      | 4.2.2            | Experimental Results                                                                                                                                                              | 143 |

|   | 4.3  |                  | Biased 45 $\mu$ m-Pitch AER Pixel with Temporal Differ-<br>Filtering                                                                                                              | 151 |

|   |      | 4.3.1            | Full-Custom ASIC Design                                                                                                                                                           | 151 |

|   |      | 4.3.2            | Experimental Results                                                                                                                                                              | 155 |

|   |      |                  |                                                                                                                                                                                   |     |

| 5 |      | ger To<br>hnolog | est Chips in 2.5 $\mu$ m, 0.35 $\mu$ m and 0.15 $\mu$ m CMOS                                                                                                                      | .59 |

|   | ICC  | molog            |                                                                                                                                                                                   | .03 |

|   | 5.1  |                  | v-Cost $32 \times 32$ Integrated Test Platform for Electrical cterization of Imagers $\ldots \ldots \ldots$ | 159 |

|   |      | 5.1.1            | Full-Custom ASIC Design                                                                                                                                                           | 166 |

|   |      | 5.1.2            | Experimental Results                                                                                                                                                              | 171 |

|   | 5.2  | An 80            | $\times 80$ Sub-1 $\mu$ W/pix 2kfps Smart MWIR Imager                                                                                                                             | 175 |

|   |      | 5.2.1            | Monolithic PbSe-CMOS Integration                                                                                                                                                  | 176 |

|   |      | 5.2.2            | Experimental Results                                                                                                                                                              | 180 |

|   | 5.3  | A $32 \times$    | 32 Frame-Free Compact-Pitch MWIR Imager                                                                                                                                           | 189 |

|   |      | 5.3.1            | Full-Custom ASIC Design                                                                                                                                                           | 190 |

|   |      | 5.3.2            | Experimental Results                                                                                                                                                              | 191 |

|   | 5.4  | Comp             | arison with State-of-the-Art IR Imagers                                                                                                                                           | 195 |

| 6 | Cor  | clusio           | ns 1                                                                                                                                                                              | .99 |

|   | 6.1  | Contr            | ibutions                                                                                                                                                                          | 199 |

|   | U. T | C 01101          |                                                                                                                                                                                   | -00 |

## List of Figures

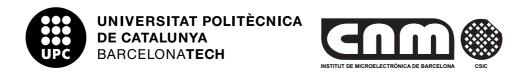

| 1.1 | General view of a staring-FPA photonic CMOS imager. Op-<br>tical sensors may be integrated in the same Si substrate, post-<br>processed on top of the CMOS dice or hybridized with the<br>ROIC. Drawing not in scale                                       | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

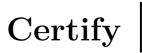

| 1.2 | Electromagnetic spectrum (a); Visible bands (b); IR bands and absorption notches (c). Adapted from [9]                                                                                                                                                     | 5  |

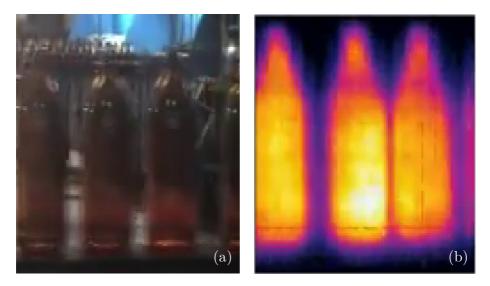

| 1.3 | Example of glass container quality inspection using visible (a) and MWIR-radiation (b) sensitive cameras [16]                                                                                                                                              | 6  |

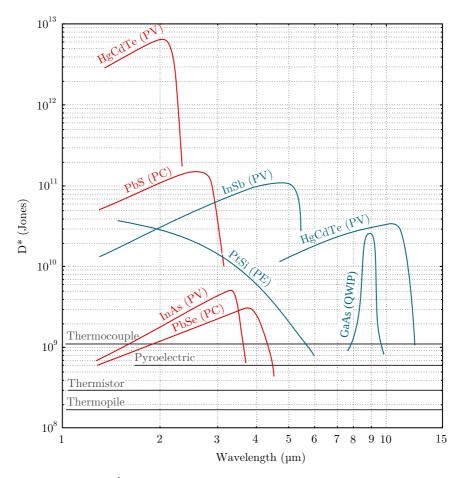

| 1.4 | Typical spectral response of main IR thermal and photon detectors at 295K room temperature (gray and red, respectively), and photon detectors at 77K cryogenic temperature (blue). Background illumination is assumed to be at a temperature of 300K [20]. | 15 |

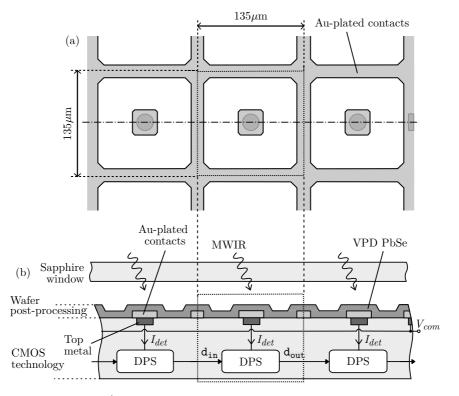

| 1.5 | Simplified layout (a) and cross-section (b) of the MWIR VPD<br>PbSe detector after being post-processed on top of its CMOS<br>wafer                                                                                                                        | 18 |

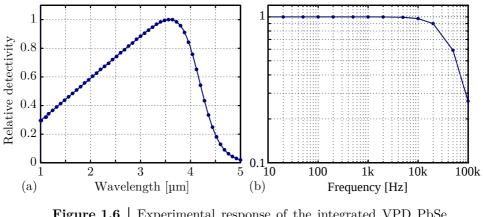

| 1.6  | Experimental response of the integrated VPD PbSe photo-<br>conductor at 300K in terms of MWIR spectral detectivity<br>(a) and modulation bandwidth (b)                                                                                       | 19 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

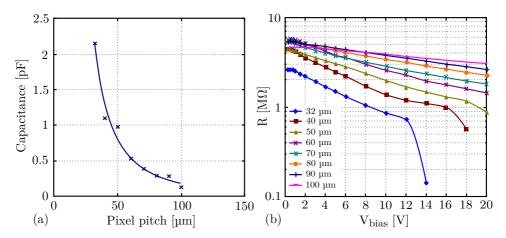

| 1.7  | Experimental output capacitance versus pixel size (a); dark<br>resistance versus bias potential for several pixel pitch values<br>(b) of the VPD PbSe photoconductor                                                                         | 20 |

| 1.8  | Experimental noise of the VPD PbSe photoconductor versus bias potential at 330Hz, for several pixel pitch values                                                                                                                             | 21 |

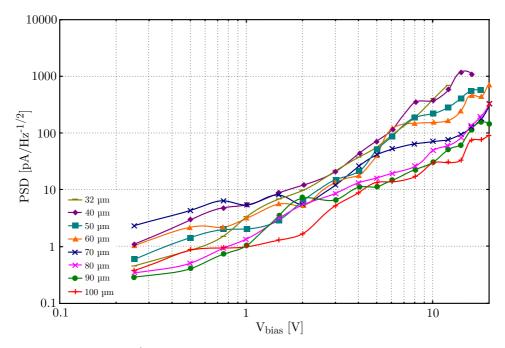

| 1.9  | Experimental noise margins of the VPD PbSe photoconductor for a fixed pitch of $40\mu$ m and an applied bias potential of $1V$                                                                                                               | 21 |

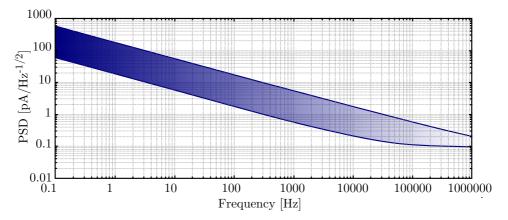

| 1.10 | VPD PbSe detector circuit equivalent (a) and schematic view (b)                                                                                                                                                                              | 23 |

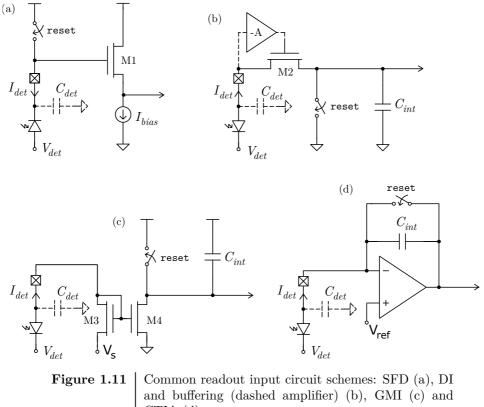

| 1.11 | Common readout input circuit schemes: SFD (a), DI and buffering (dashed amplifier) (b), GMI (c) and CTIA (d)                                                                                                                                 | 26 |

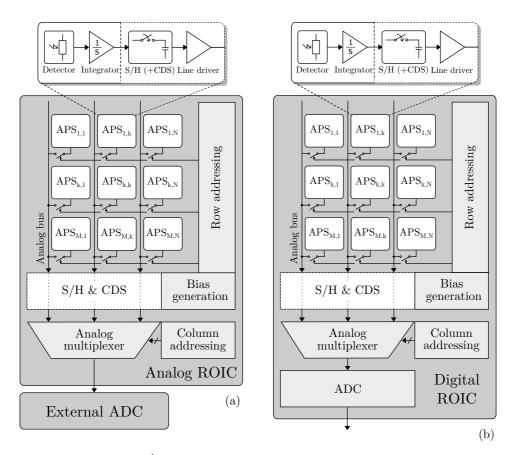

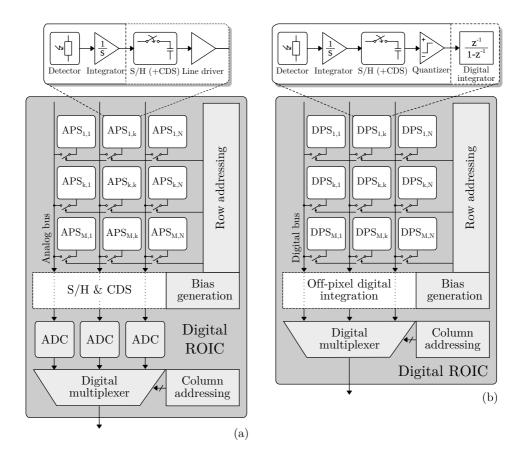

| 1.12 | Classic chip-level external (a) and internal (b) ADC readout<br>architectures. Dashed lines indicate variable circuit location:<br>S/H, CDS and buffering can be moved outside the FPA in<br>order to lessen pixel dimensions.               | 28 |

| 1.13 | Typical column-level (a) and pixel-level (b) ADC readout ar-<br>chitectures. Dashed lines indicate variable circuit location:<br>S/H, CDS, buffering and digital integration can be moved<br>outside the FPA in order to compact pixel pitch | 29 |

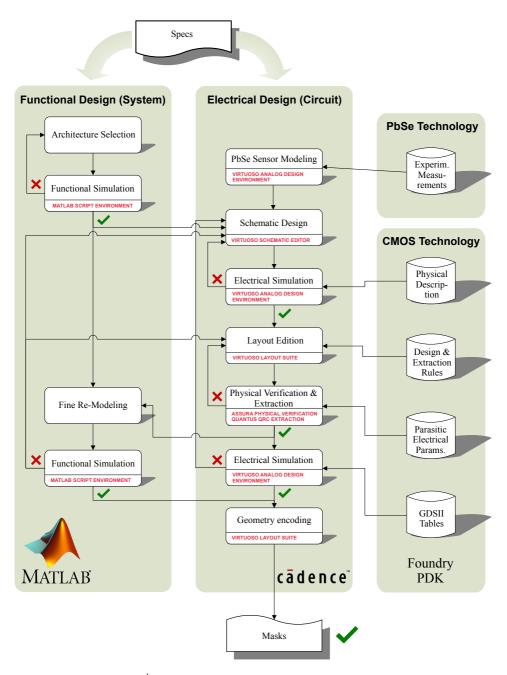

| 1.14 | Full-custom ASIC EDA design flow used in this work                                                                                                                                                                                           | 42 |

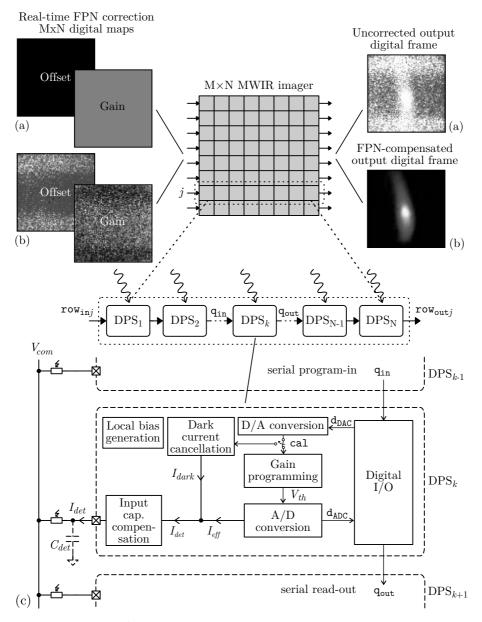

| 2.1  | Frame-based IR imager proposal. Practical examples of raw imaging under no FPN compensation (a) and in-pixel FPN-corrected aquisition (b). General DPS architecture (c). Figure not in scale                                                 | 45 |

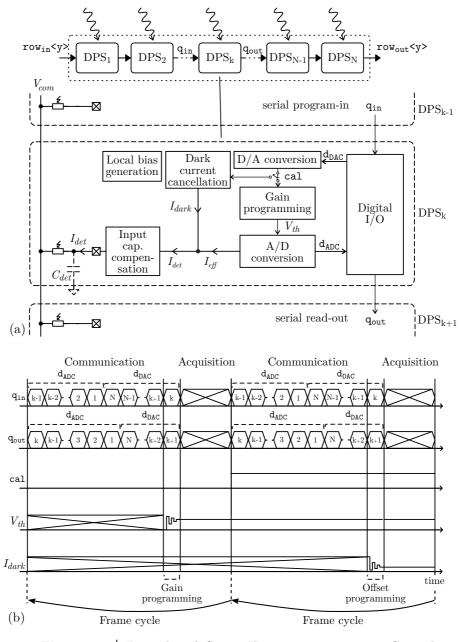

| 2.2  | Frame-based Smart IR imager operation. General DPS ar-<br>chitecture (a) and operational chronogram (b)                                                                                                                                      | 46 |

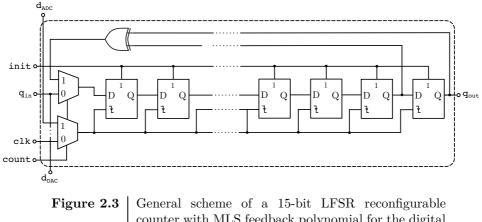

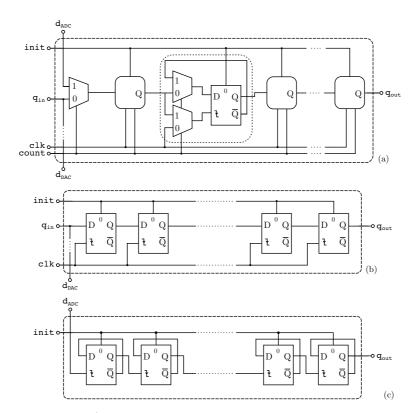

| 2.3  | General scheme of a 15-bit LFSR reconfigurable counter with MLS feedback polynomial for the digital I/O interface of Fig. 2.1. When low, control signal <b>count</b> fixes the module to behave as a shift register   | 48 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

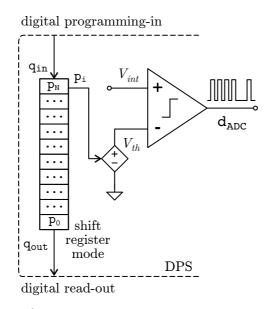

| 2.4  | Reconfigurable digital I/O interface scheme proposal for the DPS of Fig. 2.1(a). Internal configuration for communication (b) and acquisition (c)                                                                     | 49 |

| 2.5  | Full-scale transitions (black) and additional transistors (red) in reconfigurable ripple (solid line) and PRMLS (dashed line) counters. Values for 7 to 15-bit design cases.                                          | 50 |

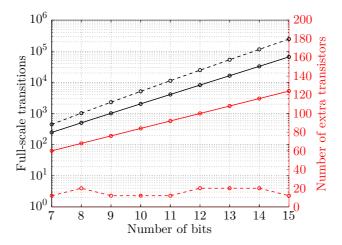

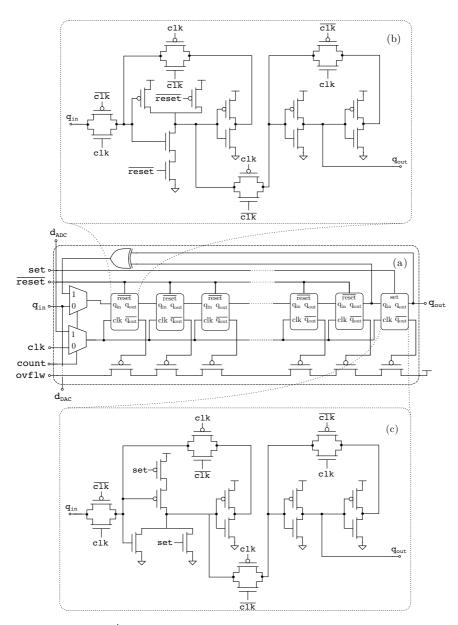

| 2.6  | Reconfigurable basic building block of the LFSR-based I/O interface with overflow detection (a). CMOS implementation of each bit register, with external initialization of type reset (b) and set (c).                | 52 |

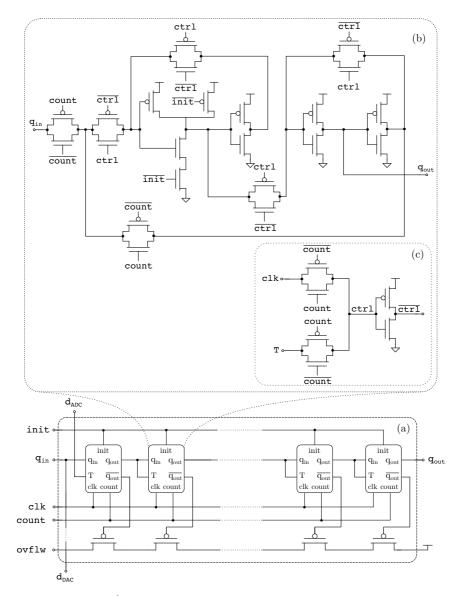

| 2.7  | Reconfigurable basic building block of the ripple-counter based I/O interface with overflow detection (a). CMOS implemen-<br>tation of each bit register (b) and signal multiplexing for T-<br>like functionality (c) | 53 |

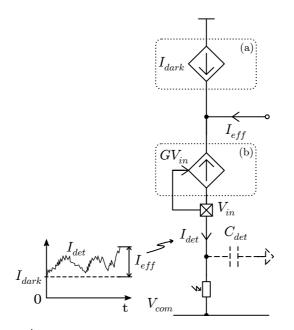

| 2.8  | Linear model of the DPS input stage proposal with dark cur-<br>rent cancellation (a) and input capacitance compensation (b)<br>for the frame-based Smart imager of Fig. 2.1                                           | 55 |

| 2.9  | DPS parasitic capacitance compensation circuit (a) and de-<br>tailed CMOS implementation for Fig. 2.8(b)                                                                                                              | 56 |

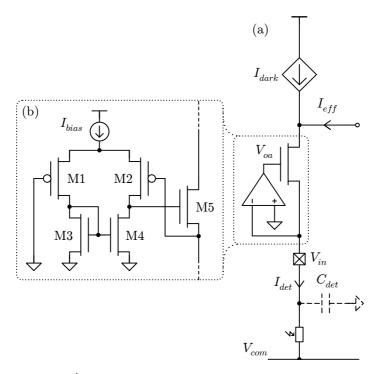

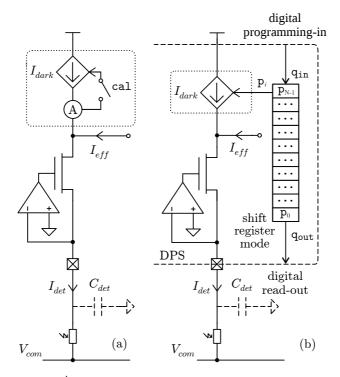

| 2.10 | DPS offset cancellation schemes: analog self-calibration (a) and digital external tuning (b)                                                                                                                          | 58 |

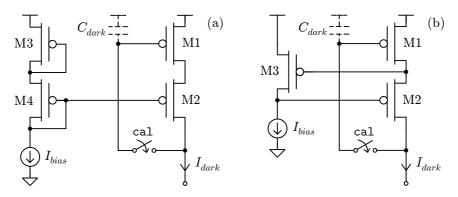

| 2.11 | CMOS circuit implementation of the DPS offset self-calibration scheme of Fig. 2.10 with simple (a) and regulated (b) cascode toppologies.                                                                             | 58 |

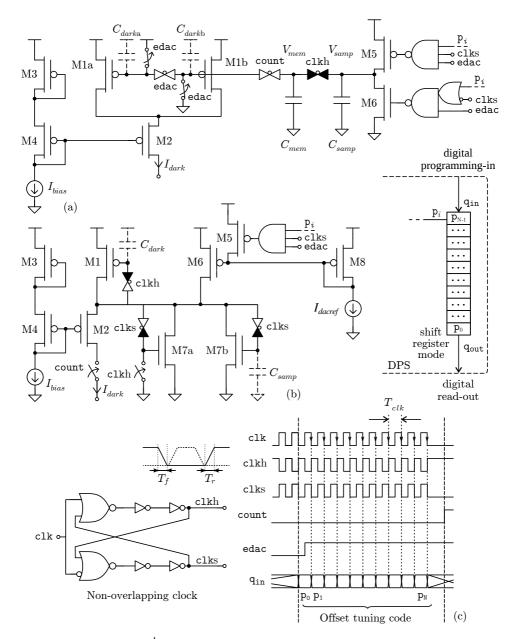

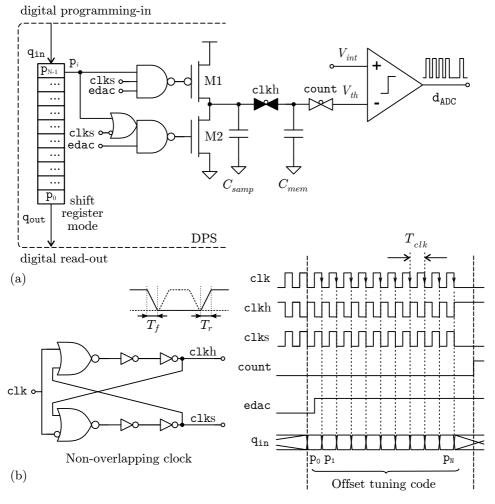

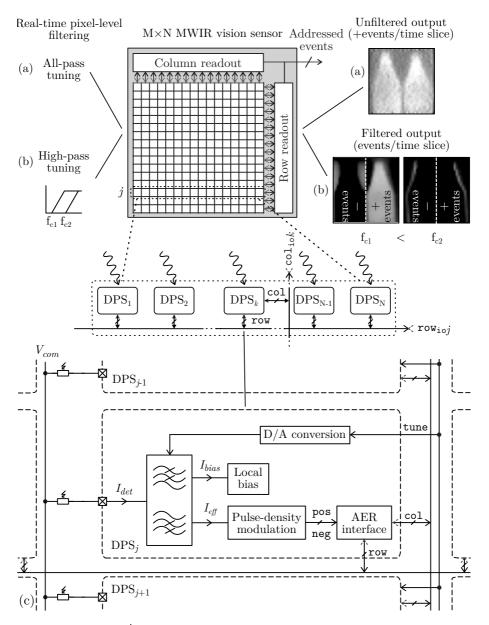

| 2.12 | DPS input stage offset cancellation with external tuning for<br>Fig. 2.10(b): CMOS DAC implementation in voltage (a) and<br>current (b). Non-overlapping clock circuit and chronogram<br>used in both schemes (c). Black filling in transmission gates<br>indicates side includes a dummy device. All signals are active<br>high | 60 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

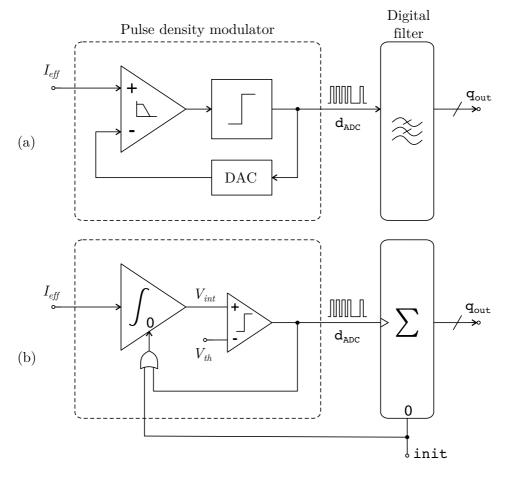

| 2.13 | General scheme of a first-order PDM predictive ADC (a) and adaptation to frame-based DPS cells (b).                                                                                                                                                                                                                              | 65 |

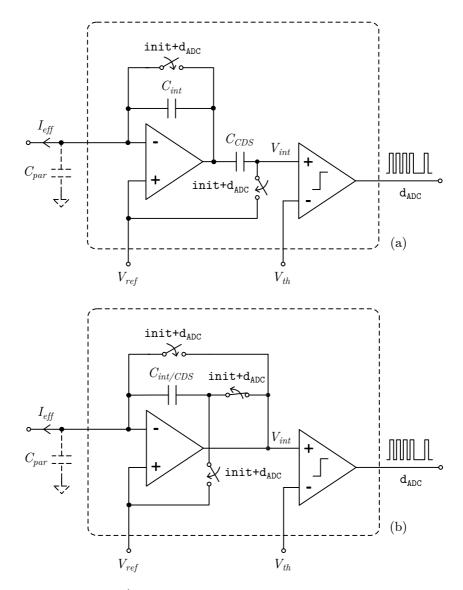

| 2.14 | Classical scheme (a) and single-capacitor integration/CDS proposal (b) for the PDM part of the in-pixel integrate-and-fire ADC ( $I_{eff} > 0$ case) of Fig. 2.13                                                                                                                                                                | 66 |

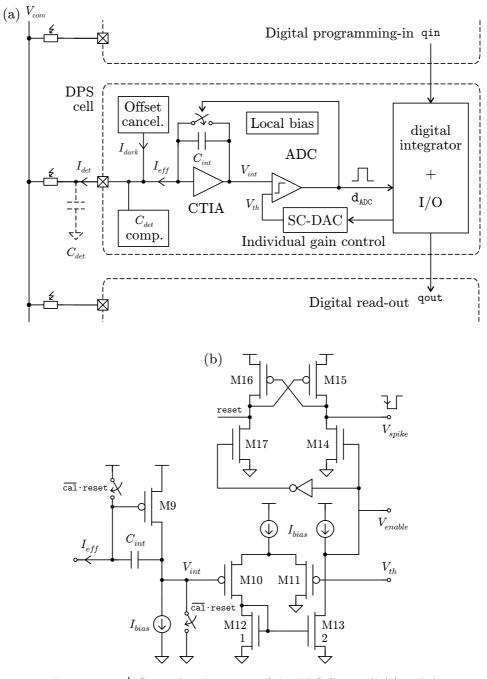

| 2.15 | DPS CMOS implementation of the analog integrator (a) in Fig. 2.14(b) and operation in reset (b) and acquisition (c) phases                                                                                                                                                                                                       | 69 |

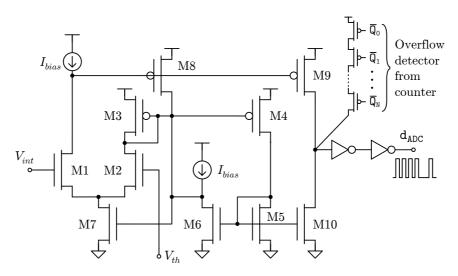

| 2.16 | DPS CMOS comparator implementation as part of the PDM modulator of Fig. 2.14(b)                                                                                                                                                                                                                                                  | 69 |

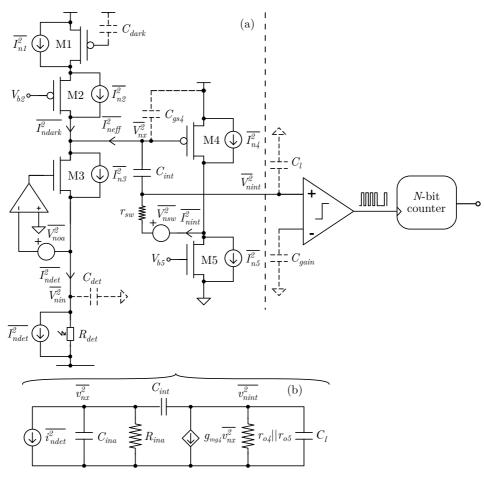

| 2.17 | Complete asynchronous ADC signal path of frame-based DPS cells during acquisition phase. Input charge integrating scheme including noise sources (a) and equivalent small-signal noise model (b).                                                                                                                                | 70 |

| 2.18 | General scheme of the individual gain tuning proposal for the in-pixel PDM ADC of Fig. 2.14(b)                                                                                                                                                                                                                                   | 78 |

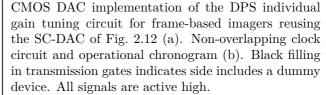

| 2.19 | CMOS DAC implementation of the DPS individual gain tun-<br>ing circuit for frame-based imagers reusing the SC-DAC of<br>Fig. 2.12 (a). Non-overlapping clock circuit and operational<br>chronogram (b). Black filling in transmission gates indicates<br>side includes a dummy device. All signals are active high               | 79 |

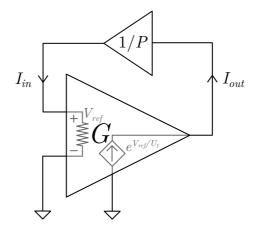

| 2.20 | PTAT reference architecture proposal for the local bias gen-<br>eration in frame-based DPS of Fig 2.1.                                                                                                                                                                                                                           | 81 |

| 2.21 | CMOS implementation of the DPS PTAT local bias generator based on the log companding architecture of Fig. 2.20                                                                                                                                                                                                                   | 82 |

|      |                                                                                                                                                                                                                                                                                                                                  |    |

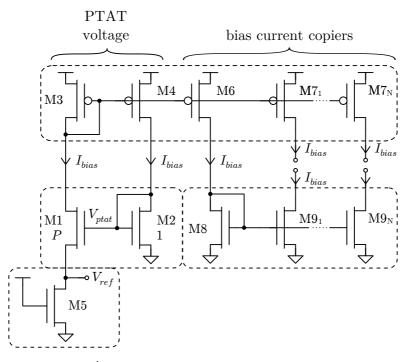

| 3.1  | Frame-free Compact-pitch IR imager proposal. Practical examples of raw (a) and low-pass filtered output imaging (b). General DPS architecture (c). Figure not in scale 87                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

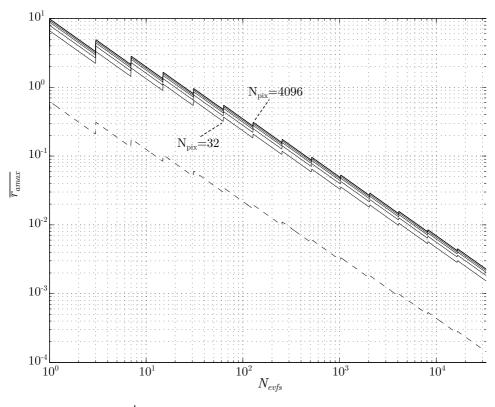

| 3.2  | $r_{amax}$ vs. $N_{evfs}$ from 32 to 2048-pixel binary FPA sizes and $N_{out} = 32$ pads. Direct readout (solid line) and column encoding (dashed line)                                                                                                                                               |

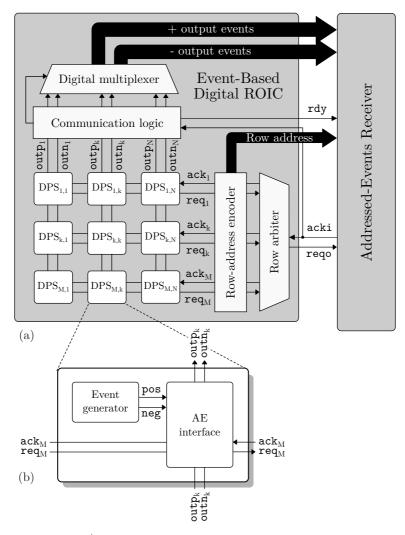

| 3.3  | Row-addressed parallel column-readout block diagram for the $M \times N$ MWIR imager of Fig. 3.1 (a) and in-pixel signaling detail (b)                                                                                                                                                                |

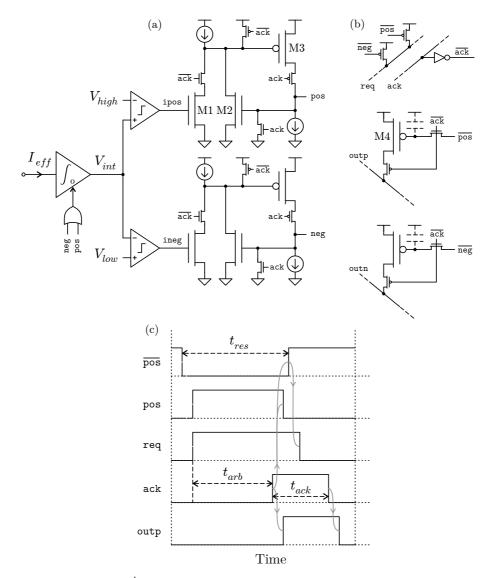

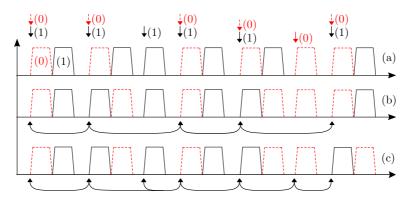

| 3.4  | CMOS implementation of the in-pixel AER communication<br>interface depicted in Fig. 3.3: high-speed state-holding com-<br>parator (a), pull-up handshaking circuit (b) and operation<br>for $I_{eff} < 0$ (c). Small MOSFET symbols correspond to<br>minimum size devices. Chronogram not in scale 94 |

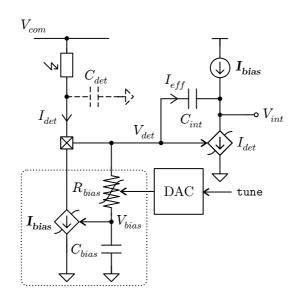

| 3.5  | General scheme of the self-biasing and TD filtering proposal<br>for the frame-free Compact-pitch imager of Fig. 3.1 96                                                                                                                                                                                |

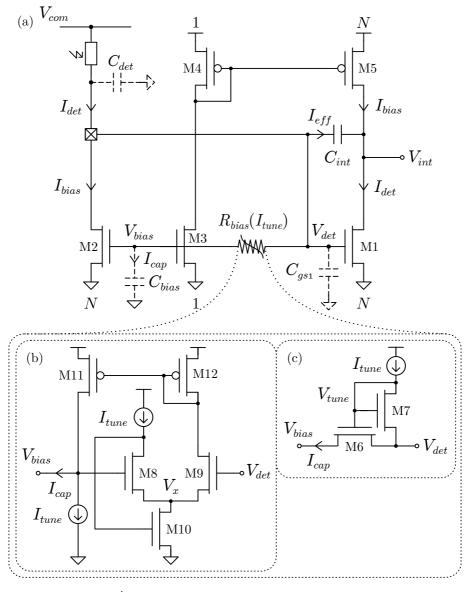

| 3.6  | Simplified CMOS schematic of the proposed circuit for DPS self-biasing and TD filtering of Fig. 3.5 (a). GD (b) and SD (c) implementations for the non-linear resistor $R_{bias}$ 98                                                                                                                  |

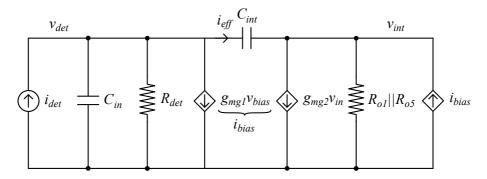

| 3.7  | Simplified small-signal model of the log-domain filtering circuit of Fig. 3.6(a)                                                                                                                                                                                                                      |

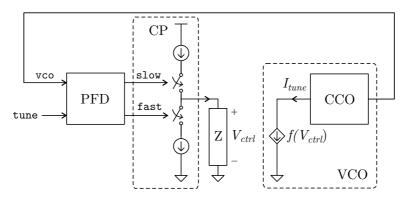

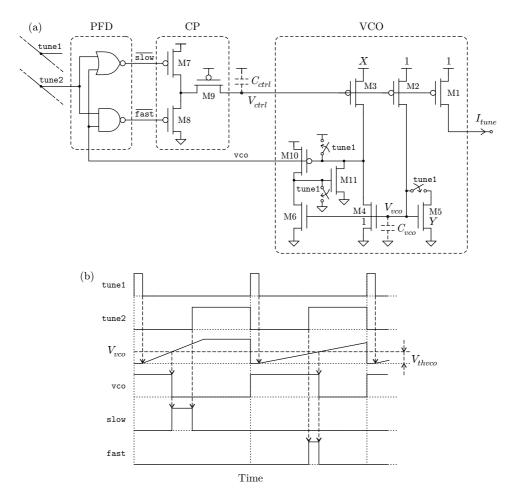

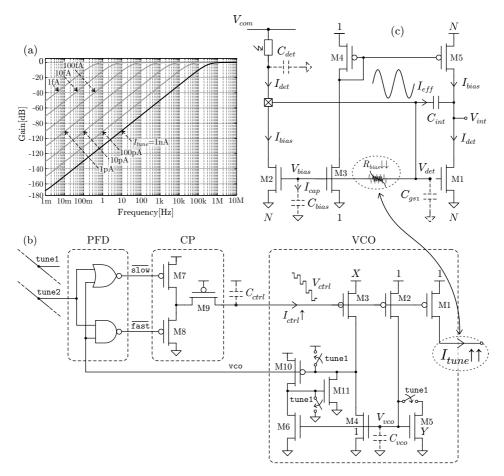

| 3.8  | PLL-based proposal for the dynamical tuning of the log-<br>domain filter in the frame-free Compact-pitch imager of Fig. 3.1.104                                                                                                                                                                       |

| 3.9  | Simplified CMOS schematic (a) and operation (b) for the PLL-based tuning of the log-domain low-pass filter used in Fig. 3.8                                                                                                                                                                           |

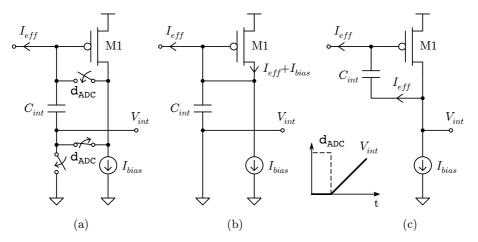

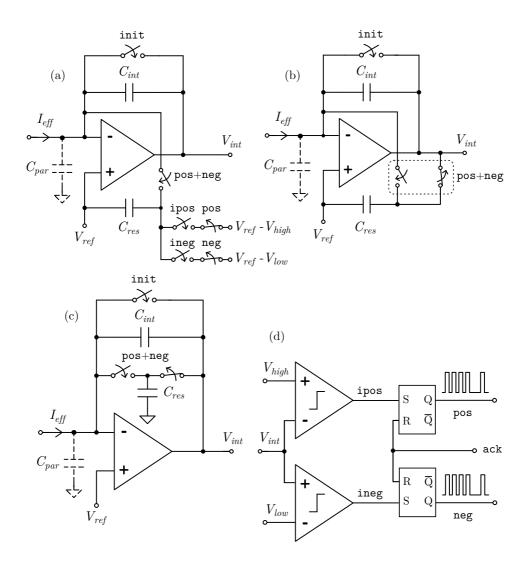

| 3.10 | Proposed lossless-reset integrate-and-fire ADC architectures<br>and comparative performance: hard-fixed charge subtraction<br>(a), and differential (b) and absolute (c) OpAmp-charged<br>subtraction. Window detection part common to all three<br>schemes (d)                                       |

#### xxiii

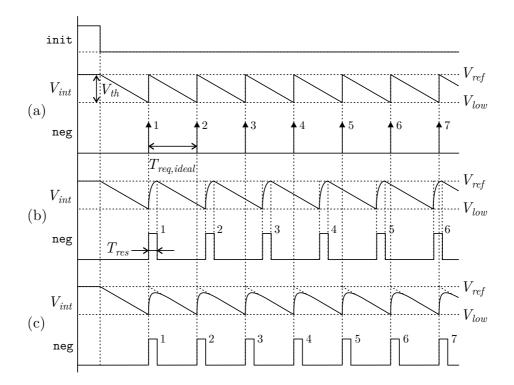

| 3.11 | Integrate-and-fire operation according to the ideal (a), clas-<br>sical (b) and proposed (c) reset schemes $(I_{eff} > 0 \text{ case})$<br>of Fig. 3.10. In this example, classical operation losses the<br>charge equivalent to 1 spike compared to ideal behavior. Fig-<br>ure not in scale                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

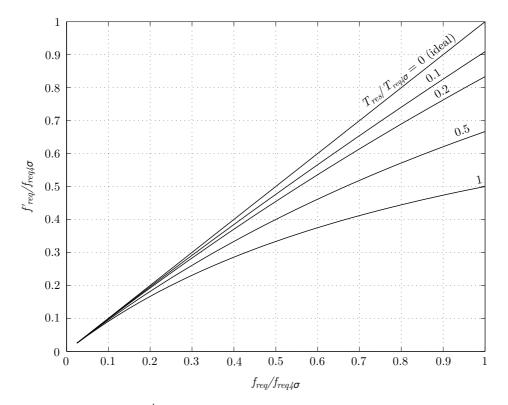

| 3.12 | Event request frequency dependency on reset time as de-<br>scribed in (3.36). Values normalized to an expected maxi-<br>mum request frequency value $f_{req4\sigma} = \overline{f_{req}} + 4\sigma(f_{req})$ 110                                                                                                               |

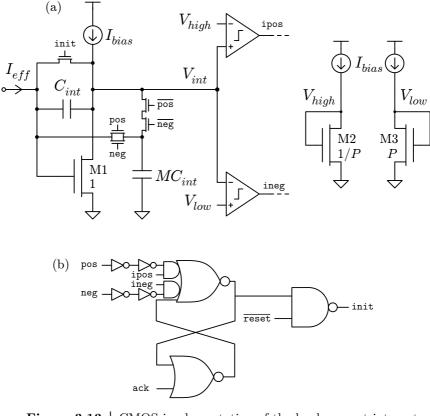

| 3.13 | CMOS implementation of the lossless-reset integrate-and-fire<br>ADC of Fig. 3.10(c) (a) and overintegration-guarding circuit<br>(b)                                                                                                                                                                                            |

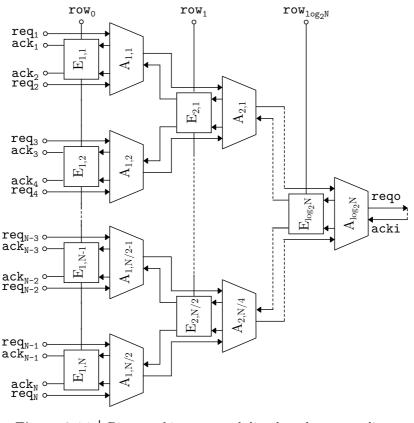

| 3.14 | Binary arbiter tree and distributed row encoding proposal for<br>the frame-free Compact-picth medium wavelength IR (MWIR)<br>vision architecture of Fig. 3.1                                                                                                                                                                   |

| 3.15 | Comparative chronogram showing event acknowledgement be-<br>tween alternative arbitration strategies: fixed priority [132]<br>(a), collision-only priority toggling [133] (b) and last-attended<br>priority toggling (this work, c). Top arrows indicate event<br>collision, double arrows causality in priority switching 115 |

| 3.16 | CMOS implementation of the basic row-encoder (a) and arbiter (b) cells, and the programmable pull-down NAND gate used in the design of the latter (c)                                                                                                                                                                          |

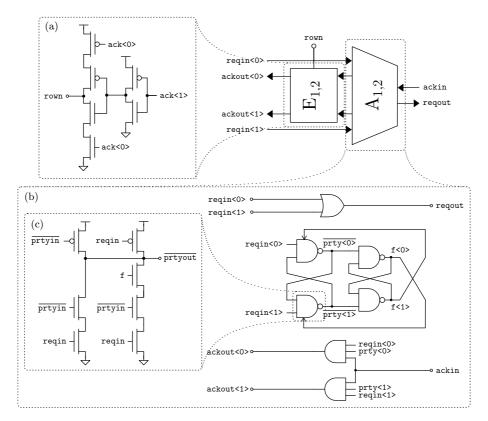

| 4.1  | General architecture of the DPS-S100 cell (a) and detail of simplified CMOS PDM implementation (b)                                                                                                                                                                                                                             |

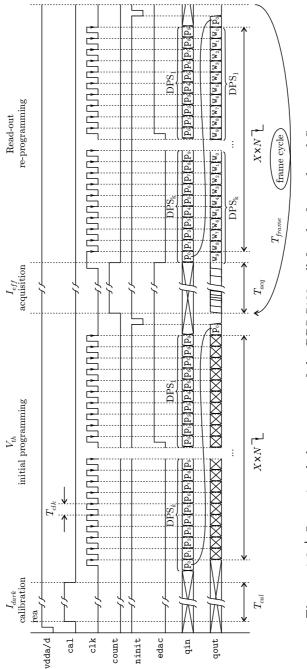

| 4.2  | Operational chronogram of the DPS-S100 cell for the frame-<br>based Smart imager of Fig. 4.1                                                                                                                                                                                                                                   |

| 4.3  | General recommendations for CMOS device matching. Reprinted with permission from [95]                                                                                                                                                                                                                                          |

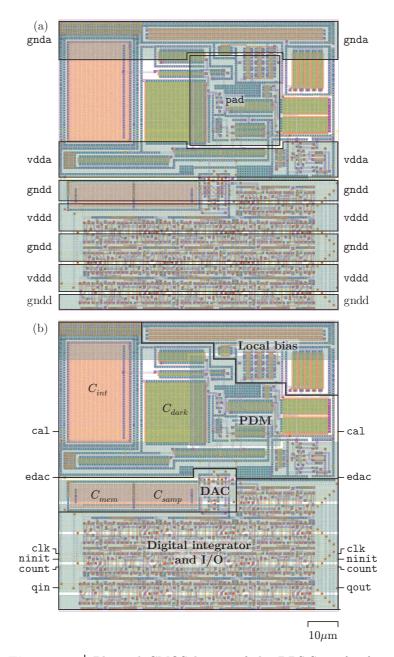

| 4.4  | Physical CMOS layout of the DPS-S100 for frame-based Smart imagers. Metal-4 power-line routing (a); metal-3 routing of control signals and main block allocation (b)                                                                                                                                                           |

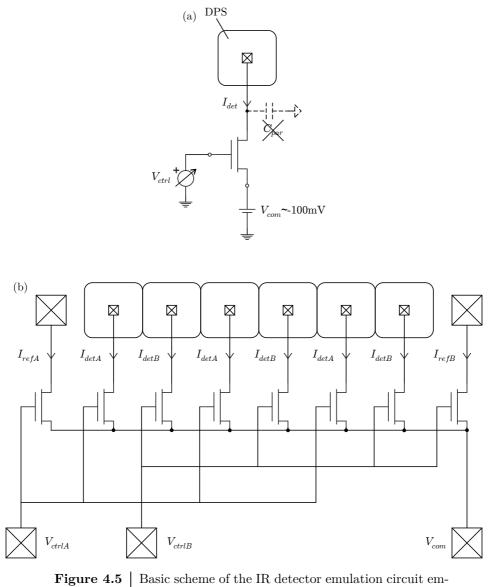

| 4.5  | Basic scheme of the IR detector emulation circuit employed<br>in the characterization of Smart DPS cells (a) and stimulus<br>distribution in the mini-FPA (b)                                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

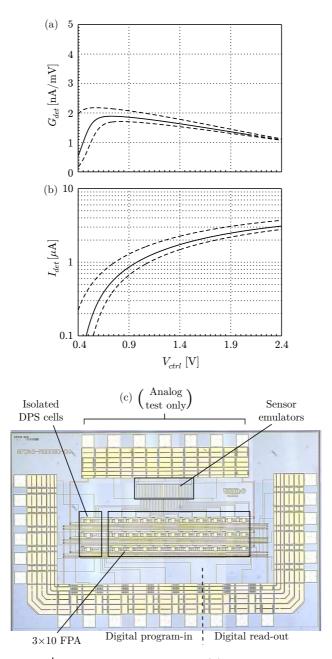

| 4.6  | Experimental sensitivity (a) and absolute current levels (b) of<br>the NMOS detector emulator included in test chips (dashed<br>lines indicate process corners). Micrograph of the test chip<br>fabricated to characterize $100\mu$ m-pitch frame-based Smart<br>digital pixel sensor (DPS-S100) cells (c) |

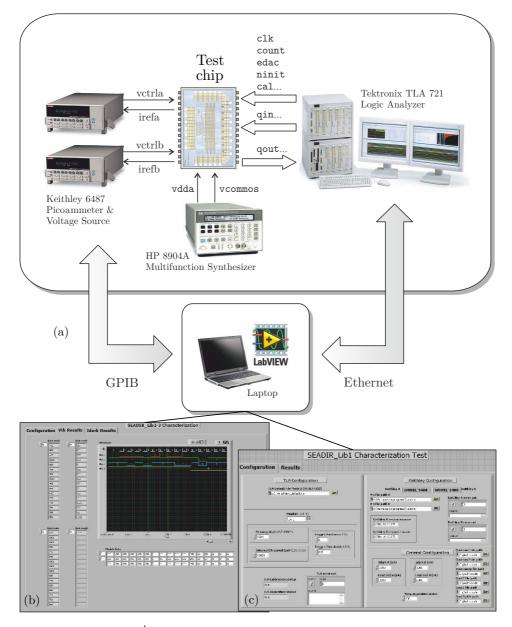

| 4.7  | Simplified scheme of the electrical testbench deployed for the electrical characterization of DPS-S cells (a). Read-out captures (b) and Labview interface front panel (c)                                                                                                                                 |

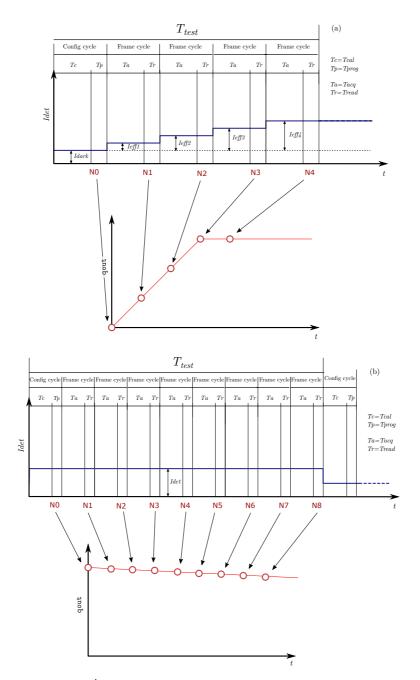

| 4.8  | Transfer memory (a) and $I_{dark}$ memory retention (b) charac-<br>terization protocols for frame-based Smart digital pixel sen-<br>sor (DPS-S) cells                                                                                                                                                      |

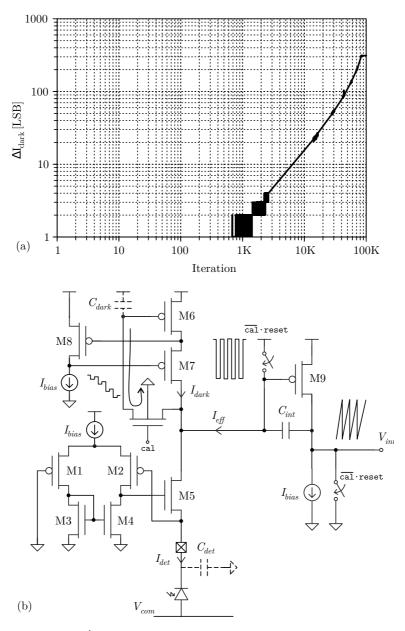

| 4.9  | Experimental measurements of $I_{dark}$ memory retention in DPS-S100 cells of Fig. 4.6(c) (a), and illustration of possible sources (b), for $I_{dark} = 1\mu A$ and $I_{eff} = 0.5\mu A$ 134                                                                                                              |

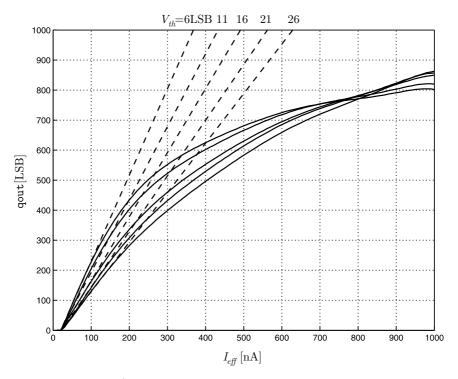

| 4.10 | Examples of experimental transfer functions for different gain<br>control values over a DPS-S100 cell of Fig. 4.6(c), for $I_{dark} = 1\mu A. \dots 135$                                                                                                                                                   |

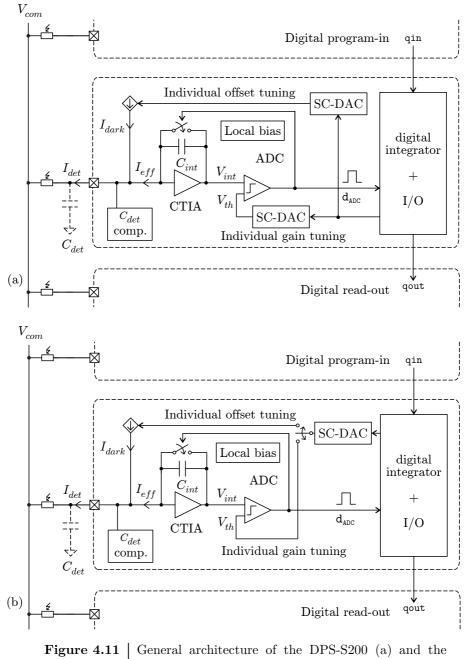

| 4.11 | General architecture of the DPS-S200 (a) and the DPS-S130 (b)                                                                                                                                                                                                                                              |

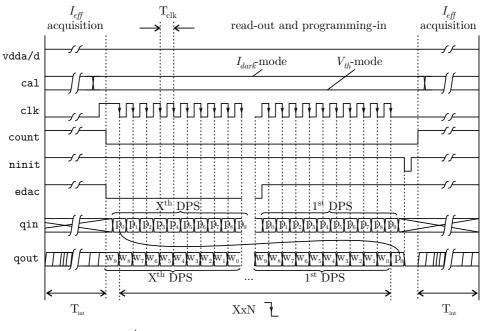

| 4.12 | Operational chronogram of DPS-S200 and DPS-S130 cells for frame-based Smart imagers                                                                                                                                                                                                                        |

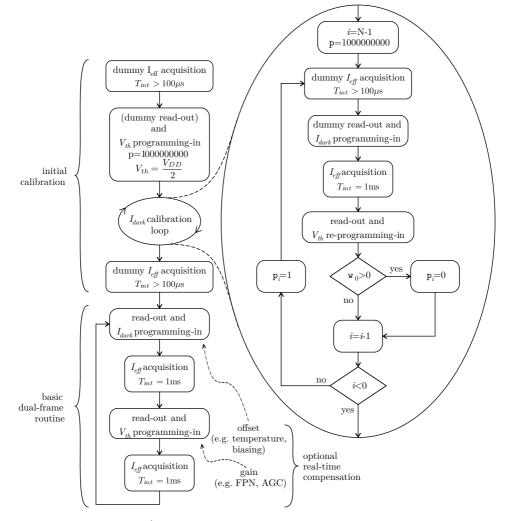

| 4.13 | Standard operating routine of DPS-S200 and DPS-S130 cells for frame-based Smart imagers                                                                                                                                                                                                                    |

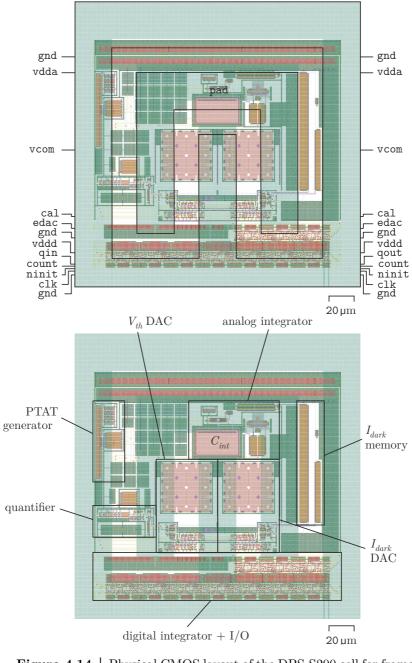

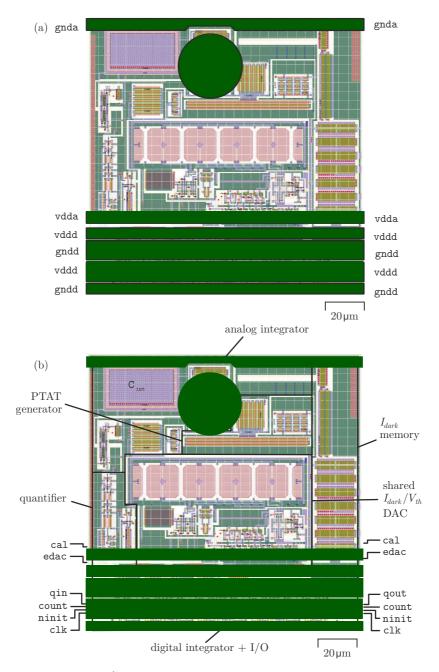

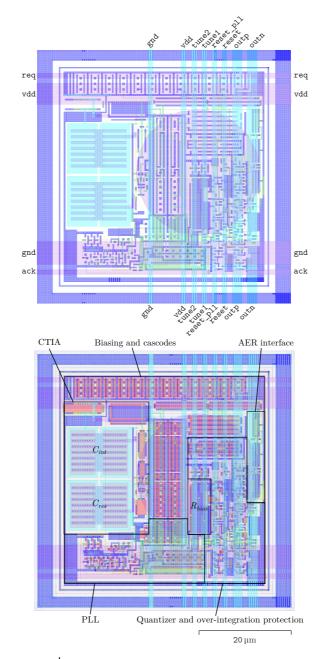

| 4.14 | Physical CMOS layout of the DPS-S200 cell for frame-based<br>Smart imagers. External interconnections (a) and main block<br>allocation (b)                                                                                                                                                                 |

| 4.15 | Physical CMOS layout of the DPS-S130 cell for frame-based<br>Smart imagers. Metal-4 power-line routing (a); metal-3 rout-<br>ing of control signals and main block allocation (b) 144                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

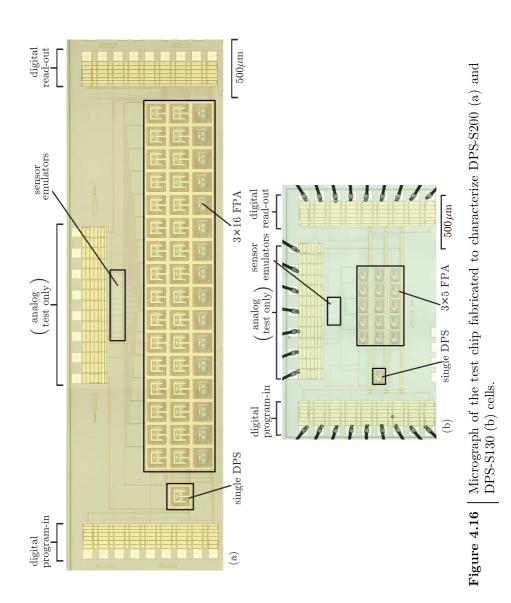

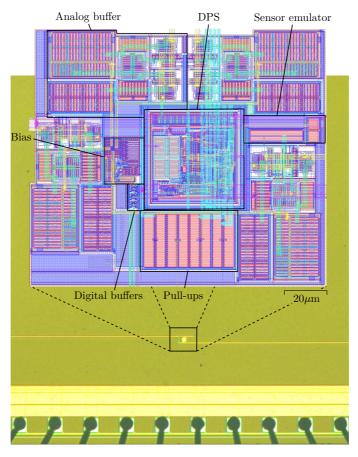

| 4.16 | Micrograph of the test chip fabricated to characterize DPS-S200 (a) and DPS-S130 (b) cells                                                                                                                                      |

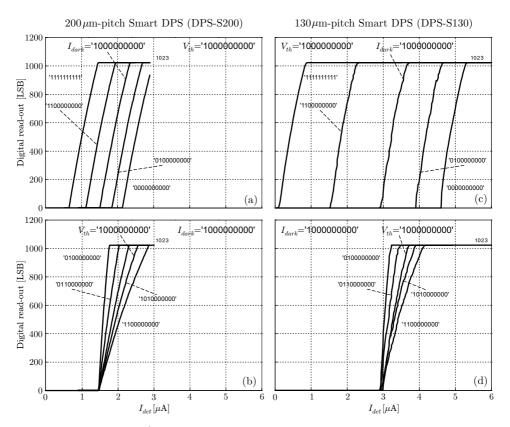

| 4.17 | Experimental transfer curve of the DPS-S200 (a,b) and the DPS-S130 cells (c,d) for different individual offset (top) and gain (bottom) digital tuning codes, respectively. $\ldots$ 146                                         |

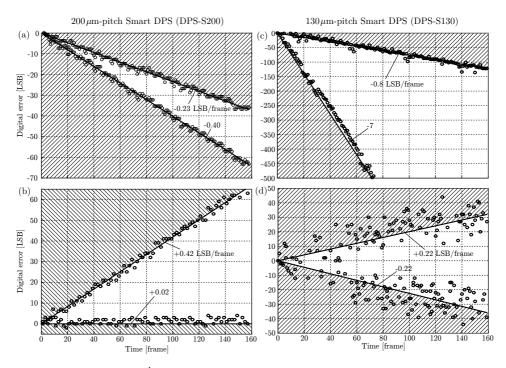

| 4.18 | Experimental range of $I_{dark}$ (a,c) and $V_{th}$ memory leakage<br>rates (b,d) inside the DPS-S200 and the DPS-S130 cells, re-<br>spectively, in terms of digital output error when only the<br>other parameter is refreshed |

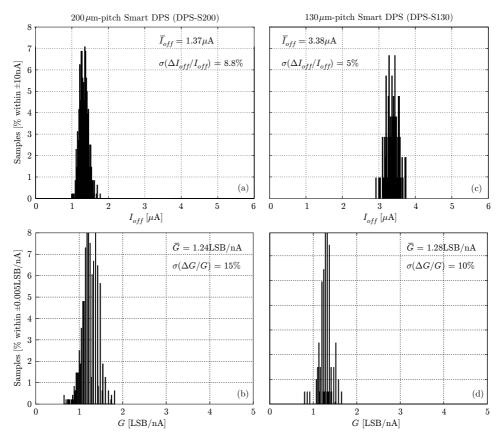

| 4.19 | Experimental offset (a,c) and gain (b,d) deviations between 480 DPS-S200 and 105 DPS-S130 cells for the digital tuning codes $I_{dark} =$ '1000000000' and $V_{th} =$ '100000000' 149                                           |

| 4.20 | Proposed architecture for the DPS-C45 cell                                                                                                                                                                                      |

| 4.21 | CMOS layout of the DPS-C45 cell. Metal usage and I/O pin location in the AER pixel (a) and main block allocation (b) 154 $$                                                                                                     |

| 4.22 | Physical CMOS layout of the test cell for the internal char-<br>acterization of the DPS-C45                                                                                                                                     |

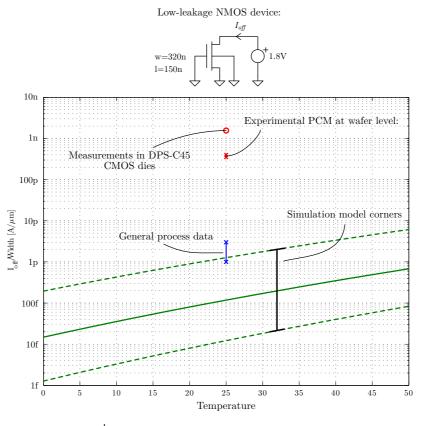

| 4.23 | Experimental measurements vs. process reported leakage values for the CMOS technology adopted in the design of the DPS-C45                                                                                                      |

| 4.24 | Simulated log-domain high-pass filtering at room tempera-<br>ture (a) and critical effects of high-leakage devices on the<br>functionality of the PLL (b) and TD (c) blocks of the DPS-C45<br>of Fig. 4.21                      |

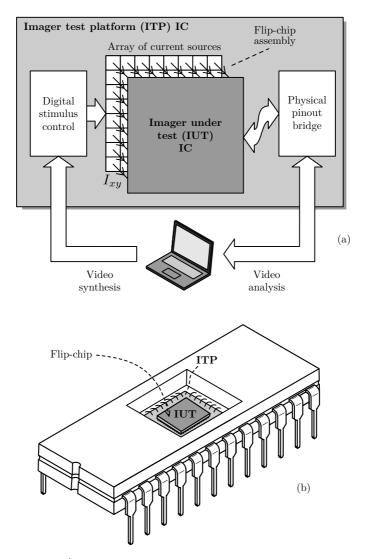

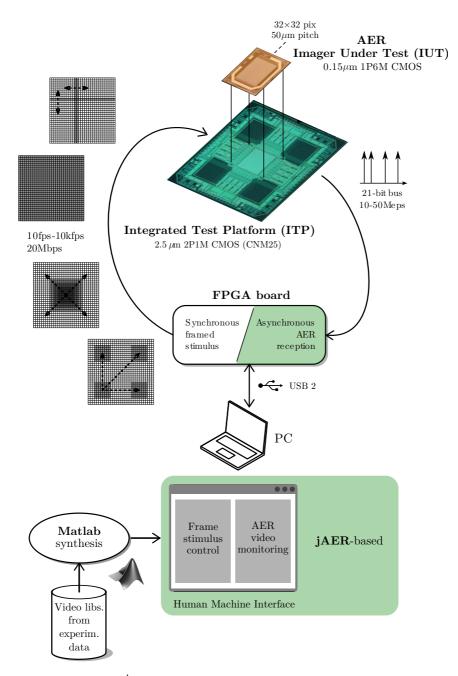

| 5.1  | Functional (a) and physical (b) description of the ITP concept.161                                                                                                                                                              |

|      |                                                                                                                                                                                                                                 |

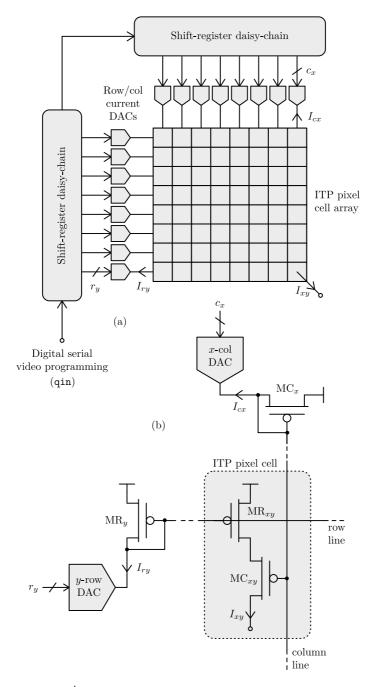

| 5.2  | ITP architecture (a) and pixel cell with and row and column controls (b)                                                                                                                                                        |

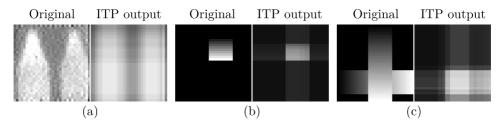

| 5.3  | Examples of digital image synthesis using the proposed ITP for real life scenes (a) and regular patterns (b,c) using 16-level DACs. Image size is $32 \times 32$                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

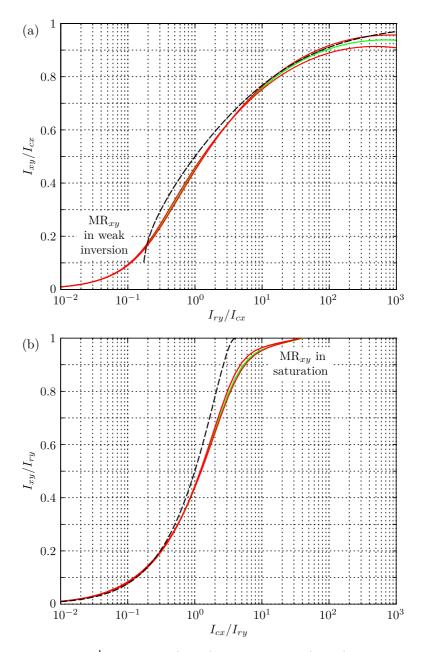

| 5.4  | Analytical (black) versus typical (green) and corner (red) electrical simulations of the ITP pixel current for $I_{cx} = 1\mu A$ (a) and $I_{ry} = 1\mu A$ (b). Supply voltage is $+5V \dots \dots \dots 165$              |

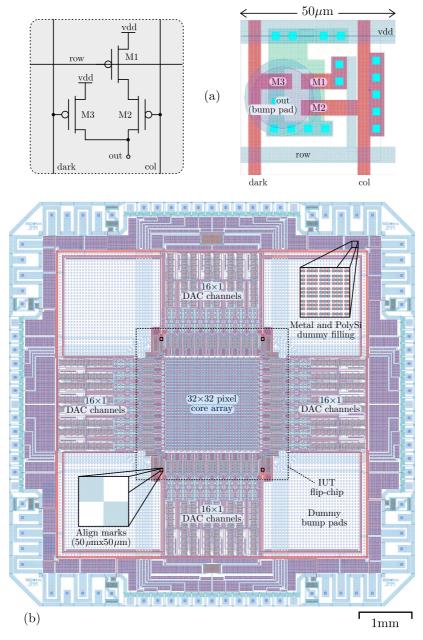

| 5.5  | Pixel cell (a) and physical CMOS layout (b) of the ITP chip.<br>Pixel bounding box is $50\mu m \times 50\mu m$ . Bump pad window di-<br>ameter is $20\mu m$                                                                |

| 5.6  | General chronogram for the digital programming of the ITP of Fig. 5.5(b). Fully parallelized case                                                                                                                          |

| 5.7  | Microscope photograph of the ITP, pinout and core array map.170                                                                                                                                                            |

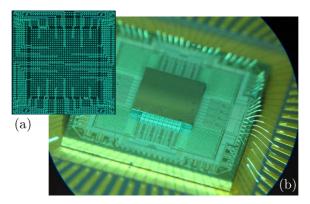

| 5.8  | Phantom IUT chip (a) attached by flip-chip to the ITP chip (b). IUT die size is $3.5$ mm $\times 3.5$ mm ( $12.3$ mm <sup>2</sup> )                                                                                        |

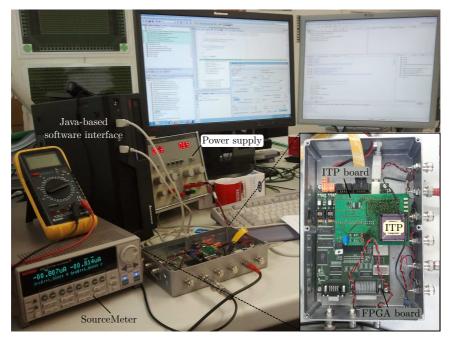

| 5.9  | Electrical characterization testbench used for the ITP chip of Fig. 5.8(b) and the IUT chip of Fig. 5.27                                                                                                                   |

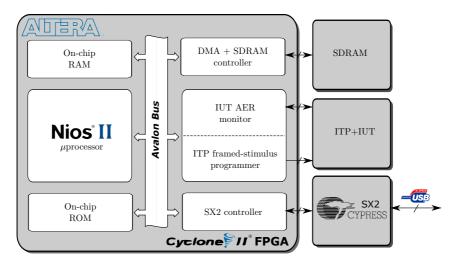

| 5.10 | FPGA configuration employed to evaluate the ITP chip of Fig. 5.8(b) and the IUT chip of Fig. 5.27                                                                                                                          |

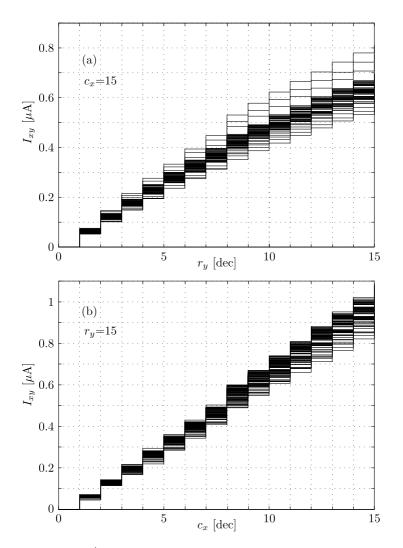

| 5.11 | Measured ITP pixel current curves versus digital row (a) and column (b) programming for $I_{bkgd} = 0$ and $I_{fs} = 1\mu A.$ 173                                                                                          |

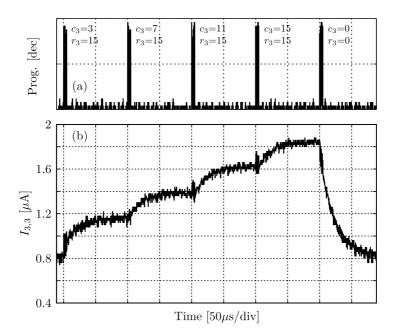

| 5.12 | Example of dynamic programming at 12.5Mbps (a) and gen-<br>erated current at 10kfps (b) of an ITP pixel (3,3) for $I_{bkgd} =$<br>$0.8\mu$ A and $I_{fs} = 1\mu$ A                                                         |

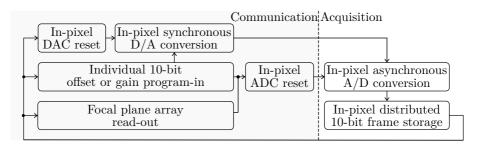

| 5.13 | Basic operation flow of the Smart IR imager                                                                                                                                                                                |

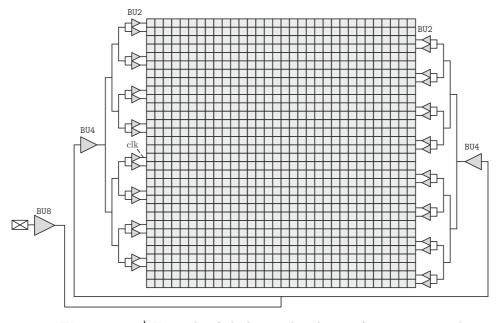

| 5.14 | Example of clock tree distribution for a $32 \times 32$ -pixel Smart<br>MWIR imager, following the same distribution that $80 \times 80$<br>FPAs. BU8, BU4 and BU2 stand for 8, 4 and 2mA digital<br>buffers, respectively |

#### xxvii

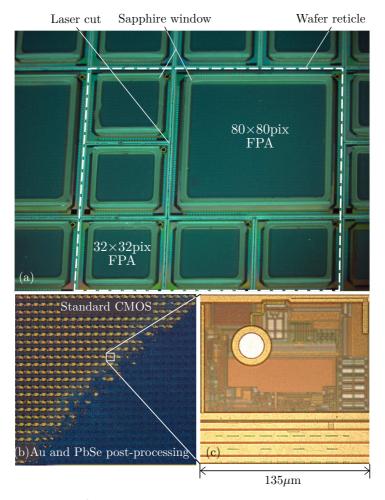

| 5.15 | Microscope photograph of the VPD PbSe post-processed wafer<br>with sapphire protection (a), FPA detail with (bottom-right)<br>and without (top-left) Au and PbSe deposited on top (b),<br>and pixel detail before post-processing (c)                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

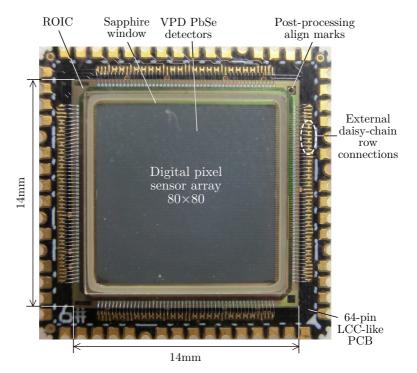

| 5.16 | Micrograph of the Smart MWIR imager fabricated in $0.35\mu$ m 2P4M CMOS technology with VPD PbSe post-processing.<br>The ROIC is directly wire bonded to chip-carrier PCB for 64-pin LCC-like sockets                                                                                                                                                                 |

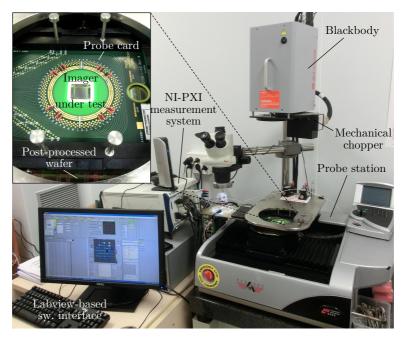

| 5.17 | Electrooptical validation setup used for imager screening at wafer level. Experimental results were obtained utilizing the same blackbody and NI-PXI measurement system                                                                                                                                                                                               |

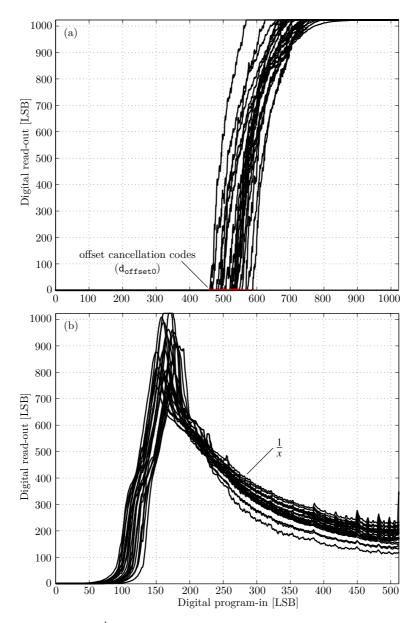

| 5.18 | Experimental offset (a) and gain (b) tuning curves of 24 DPS cells distributed over the 80×80-pixel FPA. Operating conditions are no IR illumination and $d_{gain} = 226LSB$ (a), and calibrated $d_{offset}$ to achieve $d_{out} = 512LSB$ at $d_{gain} = 226LSB$ (b). Results averaged over 150 frames from the same FPA with $\bar{\sigma}_{\bar{d}_{out}} = 4LSB$ |

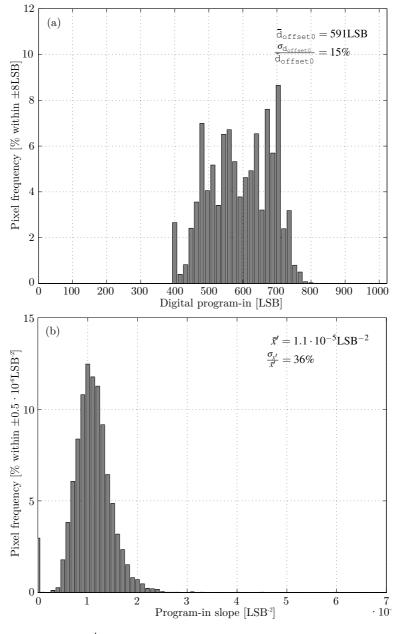

| 5.19 | Experimental deviations of offset cancellation codes (a) and gain programming slope values (b) of the 6400 DPS cells of the entire FPA of Fig. 5.16                                                                                                                                                                                                                   |

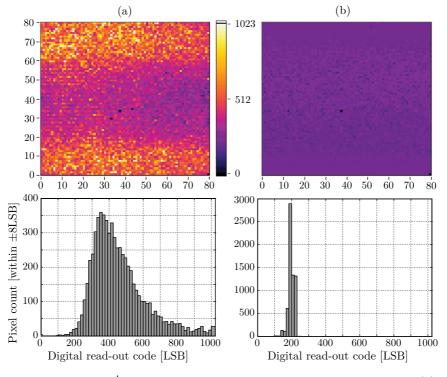

| 5.20 | Measured image and read-out dispersion before (a) and after<br>(b) in-pixel FPN equalization                                                                                                                                                                                                                                                                          |

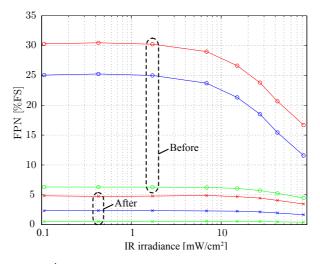

| 5.21 | Measured image pixel-to-pixel (red), row-to-row (blue) and<br>column-to-column (green) FPN versus incoming IR irradi-<br>ance before and after in-pixel FPN equalization                                                                                                                                                                                              |

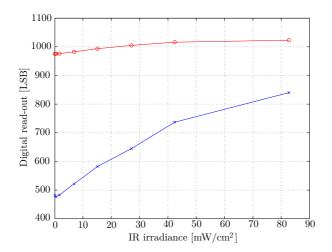

| 5.22 | Average saturated-pixel read-out values over imager focal plane<br>versus incoming IR irradiance before (red) and after (blue)<br>in-pixel equalization. Offset is calibrated at 480LSB read-out<br>in order to reach saturation                                                                                                                                      |

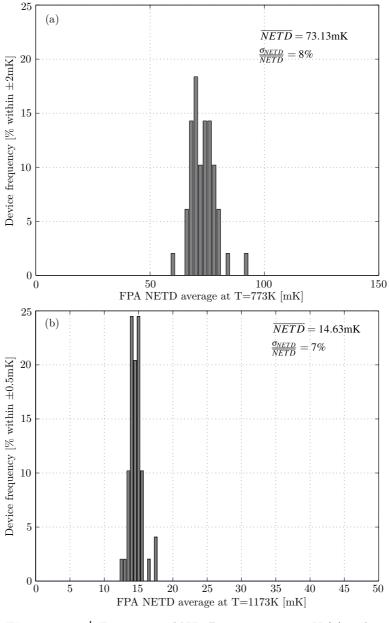

| 5.23 | Experimental NETD statistics at 773K (a) and 1173K (b) blackbody temperatures. Noise measurements are averaged for each one of the 49 imagers of an entire wafer                                                                                                                                                                                                      |

#### xxviii

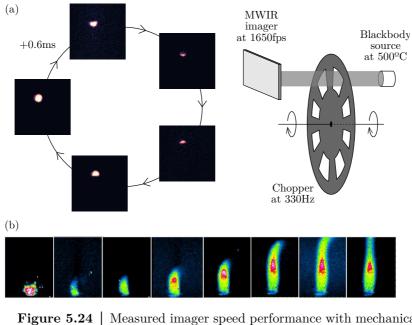

| 5.24 | Measured imager speed performance with mechanical chop-<br>per (a) and practical lighter switch-on sequence example (b). 188                                                                                                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

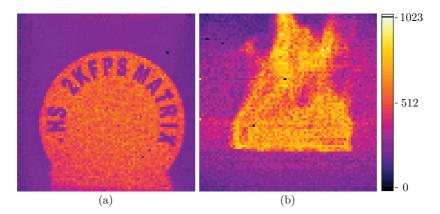

| 5.25 | Sample photograms of hot round plate (a) and flame (b) captured at 1650fps                                                                                                                                                                                                                                                    |

| 5.26 | Proposed architecture for the frame-free Compact-pitch MWIR<br>imager                                                                                                                                                                                                                                                         |

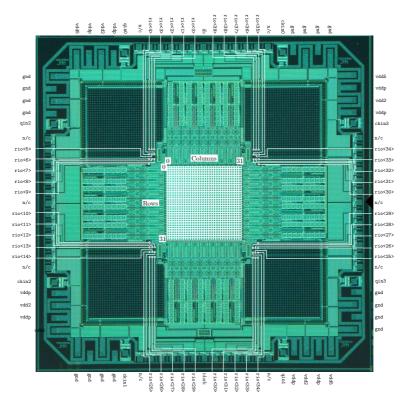

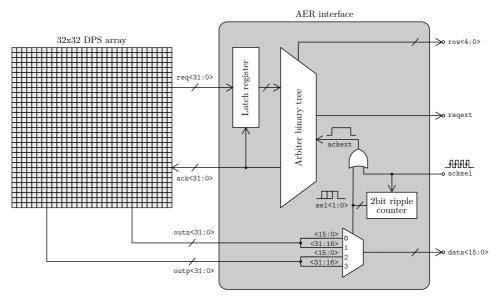

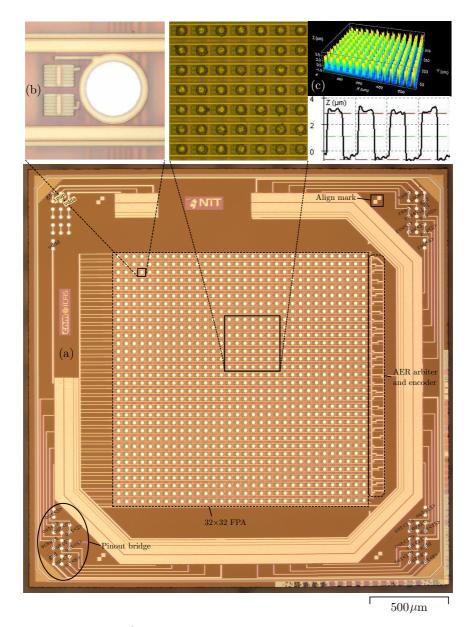

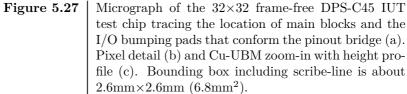

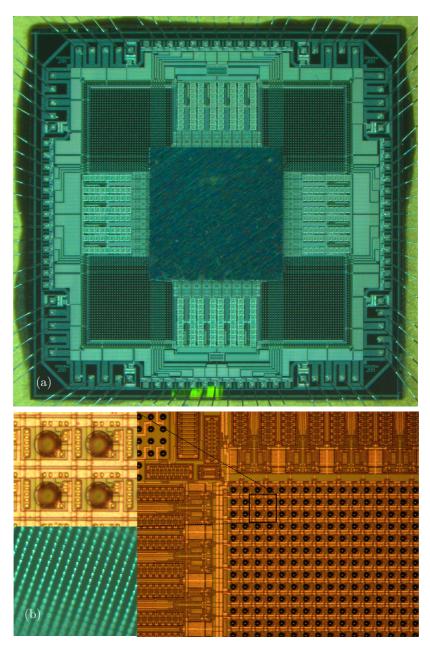

| 5.27 | Micrograph of the $32 \times 32$ frame-free DPS-C45 IUT test chip<br>tracing the location of main blocks and the I/O bumping<br>pads that conform the pinout bridge (a). Pixel detail (b)<br>and Cu-UBM zoom-in with height profile (c). Bounding box<br>including scribe-line is about 2.6mm×2.6mm (6.8mm <sup>2</sup> ) 192 |

| 5.28 | Micrograph of the complete test SIP integrated for the elec-<br>trical validation of the frame-free Compact-pitch imager of<br>Fig. 5.27 (a), and detail of the SnAg bumps grown in the<br>ITP side at wafer level (b)                                                                                                        |

| 5.29 | General scheme of the experimental setup defined for the elec-<br>trical validation of the frame-free Compact-pitch imager ar-<br>chitecture of Chapter 3                                                                                                                                                                     |

## List of Tables

| 1.1 | Overview of IR detector types and materials                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Performance and cost comparison between leading IR detec-<br>tion technologies. *Depending on temperature and detection<br>mode (i.e. PV or PC) |

| 1.3 | Typical parameters of the VPD PbSe photoconductor 20                                                                                            |

| 1.4 | Performance comparison between state-of-the-art IR vision<br>sensors                                                                            |

| 3.1 | Truth table of the arbitration unit depicted in Fig. 3.16. * means current state                                                                |

| 4.1 | Operational specifications of the industrial DPS prototypes<br>for frame-based Smart imagers                                                    |

| 4.2 | I/O diagram of the initial DPS-S100 cell for frame-based<br>Smart imagers ((P)ower, (D)igital, (I)nput, (O)utput) of Fig. 4.1.122               |

| 4.3  | Design parameters of the initial DPS-S100 cell for frame-<br>based Smart imagers of Fig. 4.1                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4  | Summary of experimental results for the DPS-S100 cells of Fig. 4.6(c)                                                                                                                                               |

| 4.5  | Measured performance of the initial DPS-S100 for frame-<br>based Smart imagers                                                                                                                                      |

| 4.6  | I/O diagram of DPS-S200 and DPS-S130 cells for frame-<br>based Smart imagers (P)ower, (D)igital, (I)nput, (O)utput) 139                                                                                             |

| 4.7  | Design parameters of both the DPS-S200 and the DPS-S130 pixels for frame-based Smart imagers of Fig. 4.15 and Fig. 4.14.143                                                                                         |

| 4.8  | Measured performance of the DPS-S200 and DPS-S130 cells<br>for frame-based Smart imagers                                                                                                                            |

| 4.9  | Operational specs of the DPS-C45 prototype for frame-free<br>Compact-pitch imagers                                                                                                                                  |

| 4.10 | I/O diagram of the DPS-C45 cell for frame-free Compact-<br>pitch imagers ((P)ower, (D)igital, (I)nput, (O)utput) 153                                                                                                |

| 5.1  | Full list of the ITP pin-out for (P)ower, (A)nalog and (D)igital types and (I)nput and (O)utput directions. The physical location of each pin and the row/column origin are defined in Fig. 5.7.                    |

| 5.2  | Performance summary of the ITP device of Fig. 5.8(b) 174                                                                                                                                                            |

| 5.3  | Full list of the frame-free IUT pin-out for (P)ower, (A)anlog<br>and (D)igital types and (I)nput and (O)utput directions. The<br>physical location of each pin and the row/column origin is<br>defined in Fig. 5.27 |

| 5.4  | Performance comparison between this work and state-of-the-<br>art IR vision sensors                                                                                                                                 |

## List of Acronyms

| AC    | alternating current                     |     |

|-------|-----------------------------------------|-----|

| AE    | adressed event                          |     |

| AER   | address event representation            |     |

| ADC   | analog-to-digital converter             | 24  |

| AGC   | automatic gain control                  |     |

| ALOHA | additive links on-line Hawaii area      | 113 |

| APS   | active pixel sensor                     | 2   |

| ASIC  | application specific integrated circuit |     |

| BDI   | buffered direct injection               | 24  |

| BGMI  | buffered gate modulation input          | 24  |

| BLIP  | background-limited infrared performance |     |

| BW    | bandwidth                               | 85  |

| CBD   | chemical bath deposition                |     |

| CCD   | charge-coupled device                   | 2   |

| ссо   | current-controlled oscillator           |     |

| CDS      | correlated double sampling                                                            |

|----------|---------------------------------------------------------------------------------------|

| CMOS     | complementary metal-oxide-semiconductor1                                              |

| CNM25    | $2.5\mu m$ 2-polySi 1-metal CMOS CNM Technology                                       |

| СР       | charge pump                                                                           |

| СТІА     | capacitive transimpedance amplifier                                                   |

| DAC      | digital-to-analog converter                                                           |

| DC       | direct current                                                                        |

| DI       | direct injection                                                                      |

| DFM      | design for manufacturability168                                                       |

| DPS      | digital pixel sensor                                                                  |

| DPS-C    | frame-free Compact-pitch digital pixel sensor                                         |

| DPS-C45  | $45\mu\mathrm{m}\text{-pitch}$ frame-free Compact-pitch digital pixel sensor .<br>151 |

| DPS-S    | frame-based Smart digital pixel sensor119                                             |

| DPS-S100 | $100\mu$ m-pitch frame-based Smart digital pixel sensor 120                           |

| DPS-S130 | $130\mu$ m-pitch frame-based Smart digital pixel sensor 137                           |

| DPS-S200 | $200\mu$ m-pitch frame-based Smart digital pixel sensor 137                           |

| EDA      | electronic design automation                                                          |

| EKV      | Enz-Krummenacher-Vittoz                                                               |

| ELIN     | externally-linear internally-nonlinear                                                |

| QE       | quantum efficiency                                                                    |

| DR       | dynamic range                                                                         |

| ESD      | electrostatic discharge168                                                            |

| FF       | fill factor                                                                           |

| FPA      | focal plane array 1                                                                   |

| FPGA     | field-programmable gate array171                                                      |

| FPN      | fixed pattern noise9                                                                  |

| FOM      | figure of merit                                                                       |

| GD       | gate-driven                                                                           |

#### xxxiv

| GMI    | gate modulation input                                      | 24  |

|--------|------------------------------------------------------------|-----|

| GPIB   | general purpose interface bus                              | 127 |

| нмі    | human-machine interface                                    | 172 |

| IC     | integrated circuit                                         | 38  |

| ITP    | integrated test platform                                   | 153 |

| IUT    | imager under test                                          | 160 |

| IR     | infrared                                                   | 1   |

| LCC    | leadless chip carrier                                      | 177 |

| LCD    | liquid crystal display                                     | 205 |

| LFSR   | linear-feedback shift register                             |     |

| LSB    | least significant bit                                      |     |

| LUT    | look-up table                                              |     |

| LVS    | layout versus schematic                                    |     |

| LWIR   | long wavelength IR                                         | 5   |

| MEMS   | micro-electro-mechanical systems                           | 3   |

| MIM    | metal-insulator-metal                                      | 153 |

| MLS    | maximum-length sequence                                    |     |

| MOS    | metal-oxide semiconductor                                  | 49  |

| MOSFET | metal-oxide-semiconductor field-effect transistor $\ldots$ | 25  |

| MPW    | multi-project wafer                                        | 175 |

| MSB    | most significant bit                                       | 50  |

| MWIR   | medium wavelength IR                                       | 5   |

| NEP    | noise equivalent power                                     | 10  |

| NIR    | near infrared                                              | 5   |

| NTF    | noise transfer function                                    | 72  |

| NETD   | noise equivalent temperature difference                    | 11  |

| NMOS   | n-channel metal-oxide-semiconductor                        | 56  |

| РС     | photoconductive                                            | 13  |

| РСВ   | printed circuit board                 |     |

|-------|---------------------------------------|-----|

| PDK   | process design kit                    |     |

| PE    | photoemissive                         | 13  |

| PIP   | polysilicon-insulator-polysilicon     | 153 |

| PRMLS | pseudo-random maximum length sequence |     |

| PV    | photovoltaic                          | 13  |

| Ρντ   | process, voltage, temperature         |     |

| OA    | operational amplifier                 | 25  |

| ODE   | ordinary differential equation        |     |

| PC    | photoconductive                       | 13  |

| РСВ   | printed circuit board                 |     |

| PDM   | pulse density modulation              |     |

| PFD   | phase-frequency detector              |     |

| PLL   | phase-locked loop                     |     |

| PM    | pulse modulation                      |     |

| PMOS  | p-channel metal-oxide-semiconductor   | 25  |

| PSD   | power spectral density                | 19  |

| ΡΤΑΤ  | proportional to absolute temperature  |     |

| PV    | photovoltaic                          | 13  |

| Ρ٧Τ   | process, voltage and temperature      |     |

| PWM   | pulse width modulation                |     |

| QWIP  | quantum well IR photodetector         | 13  |

| RMS   | root mean square                      | 8   |

| ROI   | region of interest                    |     |

| ROIC  | read-out integrated circuit           | 2   |

| SBDI  | share-buffered direct injection       |     |

| SC    | switched-capacitor                    | 62  |

| SCI   | switched-current integrator           | 24  |

| SD    | source-driven                            |    |

|-------|------------------------------------------|----|

| SDRAM | synchronous dynamic random access memory |    |

| SFD   | source follower per detector             |    |

| SI    | switched current                         |    |

| SIP   | system-in-package                        |    |

| SNR   | signal to noise ratio                    | 8  |

| STF   | signal transfer function                 | 72 |

| SWIR  | short wavelength IR                      | 5  |

| TD    | temporal difference                      |    |

| TFS   | time-to-first spike                      |    |

| тν    | television                               |    |

| UBM   | under bump metallization                 |    |

| USB   | universal serial bus                     |    |

| vco   | voltage-controlled oscillator            |    |

| VLSI  | very-large-scale integration             | 2  |

| VPD   | vapour phase deposition                  |    |

xxxviii

# Introduction 1

Infrared (IR) thermal imaging is an emerging technology with promising industrial, scientific and medical applications. The recent introduction of uncooled photonic sensors based on vapour phase deposition (VPD) PbSe technologies [2] opens the door to a new generation of high-speed and low-cost IR vision devices made of monolithic active focal plane arrays (FPAs). This thesis investigates novel complementary metal-oxidesemiconductor (CMOS) circuit design techniques and fully-digital configurable-readout architectures specially conceived to operate these detectors. In this context, the present chapter introduces the motivation, background and trends of current thermography systems, and highlights the main aims of the work.

## 1.1 Seeing Beyond the Visible

### 1.1.1 Vision Cameras

Vision, widely acknowledged as our foremost human sense, is a highly regarded resource to perceive and interact with the world that surrounds us. It is not by chance that numerous expressions like "to watch out", "to look after" or "to foresee" populate the English language and have equivalent examples in many other human cultures. But what does it mean to see something? When we are looking at a scene, our eyes capture electromagnetic radiation and convert it to electrical signals depending on the color, brightness and contrast of the image received. Visual information is then processed and interpreted in our brains as shape and motion, and used to identify objects so as to facilitate a proper behavior for survival. Guided by chance and curiosity, and attracted by the opportunity to spot distant places and times out of one's natural sight, many thinkers have contributed to apply imaging principles to the development of human-made vision sensors. It all started with the observation of the pinhole effect [3] and the creation of the camera obscura back in the fifth century B.C. [4], and continued with the invention of the first permanent photographic cameras by Niépce [5] and Daguerre [6] in the nineteenth century. These two initial discoveries triggered off 200 years of frame-based imaging revolution.

The high degree of maturity reached today by Silicon-based semiconductor technologies has bloomed into the high-resolution and portable digital cameras we can find in stores. Contemporary imagers are made of very-large-scale integration (VLSI) microelectronic devices. They include millions of transistors, placed in extremely reduced areas and capable to process millions of data per second at a very competitive price. The present generation of digital cameras is dominated by CMOS image sensors that, as predicted by [7], have been progressively gaining market share where their older charge-coupled device (CCD) relatives have lost. Prevailing are staring FPA architectures as depicted in Fig. 1.1, whose pixelated photonic detectors are monolithically or hybridly joined to an array of CMOS readout circuit cells. Every one of the resulting individual sensors that compose the focal plane is called an active pixel sensor (APS). Such CMOS read-out integrated circuit (ROIC) implementations are typically preferred because they offer:

- Reduced technological costs, if last generation of sub-micron CMOS processes are not required.

- Direct integration of mixed analog-digital circuits in the same Silicon substrate.

- Compatibility with micro-electro-mechanical systems (MEMS) structures and devices, increasing performance and reducing the cost of the complete camera integration.

- Large scalability, leading integration trends in the sector of consumer electronics [8].

Most of these devices are only sensitive to a reduced part of the electromagnetic spectrum: visible and near IR light, and provide affordable artificial vision with a spectral response slightly beyond human eye's reach. But this tendency is steadily changing. Current demand for significant strategic, industrial, scientific and medical equipment is pushing these capabilities into the deep IR range.

#### 1.1.2 Seizing the Red End

Discovered by Sir William Herschel in 1800, IR radiation refers to that located just above the red end of visible spectrum. Most of the thermal radiation emitted by objects at room temperature is in the IR range, generated or absorbed by molecules at the transition between their rotational-vibrational movements. Extending the detectable electromagnetic spectrum towards IR implies remarkable functionality gains due to both, the aforesaid capability of matter to self emit at this wavelength range and the energy information obtained from the observed materials. The former allows to see in poor lightning scenarios such as dusty and cloudy environments, or those with no external light sources like the Sun or the Moon; the latter offers valuable information, not apparent under regular visible radiation, that facilitates thermal and chemical identification. Hot objects, people and animals glare in pitch-black darkness, distant planets and stars can be examined in their early stellar days, and weaknesses are revealed in structures.

Much of the IR emission spectrum is unusable for detection systems because radiation is absorbed by water or carbon dioxide in the atmosphere. There are several wavelength bands, however, that exhibit good transmittance (Fig. 1.2):

**Figure 1.1** General view of a staring-FPA photonic CMOS imager. Optical sensors may be integrated in the same Si substrate, postprocessed on top of the CMOS dice or hybridized with the ROIC. Drawing not in scale.

- Long wavelength infrared (LWIR). This band extends roughly from 8 to 14  $\mu$ m, with nearly full transmission on the 9  $\mu$ m to 12  $\mu$ m band. LWIR offers excellent visibility of most terrestrial objects.

- Medium wavelength infrared (MWIR). This wavelength range also delivers nearly 100 % transmission in the spectrum between 3  $\mu$ m to 5  $\mu$ m, with the added benefit of lower ambient background noise.

- Short wavelength infrared (SWIR) near infrared (NIR). Also known as "reflected infrared" since light of these wavelengths are reflected by objects in a similar way than the visible spectra. Bands of high atmospheric transmission and maximum solar illumination (1  $\mu$ m to 2.5  $\mu$ m and 0.7  $\mu$ m to 1  $\mu$ m, respectively), detectors operating in these spectral ranges usually have better clarity and resolution than in the other two cases. Still, SWIR imagers need moonlight or artificial illumination in order to provide perceivable images at temperatures around 300 K.

**Figure 1.2** Electromagnetic spectrum (a); Visible bands (b); IR bands and absorption notches (c). Adapted from [9].

IR imaging is used for military and civilian purposes in all three spectral bands. Its multiple applications cover subjects as diverse as surface examination by thermography [10] (Fig. 1.3), automotive night vision [11], object tracking [12], weather forecast [13] and atomic analysis [14]. The global IR and thermal imaging market is predicted to grow from USD 3350 million in 2014 to USD 5220 million in 2019, at an estimated annual rate of 9.3% [15].

Figure 1.3 Example of glass container quality inspection using visible (a) and MWIR-radiation (b) sensitive cameras [16].

The next sections introduce the reader to the scope of this work. Sec. 1.2 reviews common metrics to evaluate the performance of IR cameras. Background on detector materials and structures used today in IR imagery is recounted in Sec. 1.3. Sec. 1.4 highlights the major characteristics of the adopted MWIR detector technology. The state-of-the-art of both FPA architectures and CMOS pixel readout techniques is presented in Sec. 1.5. This same section also enlists their operational requirements and summarizes their main modern representatives. This chapter finishes in Sec. 1.6 with a general overview of the research objectives.

# 1.2 Common Metrics and Figures of Merit

Common metrics and figure of merits (FOMs) are very useful tools to evaluate the performance of IR vision sensors, as they provide objective numeric values to compare between different design proposals. The following paragraphs review the top definitions that have been formulated along history.

**Power Density:** A typical requirement in applications using photonic FPAs. The local power (in W/pixel) dissipated by ROICs that operate this kind of detectors should be kept low to avoid undesired carrier generation effects.

**Array Size and Pitch:** Both array size and pitch are usually set by FPA technology. Higher image resolutions require larger array sizes and smaller pixel pitches. The former demand higher CMOS yields; the latter accommodate smaller integrator (charge storage) capacitances with a potential negative impact on the dynamic range figure defined below.

**Dynamic Range (DR):** The DR is defined as the power ratio of maximum signal capacity to noise floor and distortion components. The required dynamic range of imagers is determined by the ratio of the brightest to the weakest perceivable illumination level. Larger dynamic ranges are desirable but limited by storage capacitance, linearity and composite pixel noise.

Fill Factor (FF): Not all of the image sensor surface is sensitive to electromagnetic energy: each individual detector is commonly surrounded by material exclusively used to fit polarization and readout circuitry. The ratio of active sensing material to total pixel area is called the fill factor. Ideal pixel sensors have fill factors of 100% and devote all their surface to phototransduction, increasing their sensitivity and improving image quality. Today's best infrared staring-FPA cameras offer figures as high as 90%.

**Quantum Efficiency (QE):** QE is the fraction of photon flux that contributes to the total current generated by a photodetector. A crucial parameter to evaluate the quality of a detector, it is also known as spectral response due to its dependence on input radiation wavelength.

**Thermal Contrast (C):** The relative scene contrast C (given in  $K^{-1}$ ) quantifies system sensitivity to thermal radiation and is defined by (1.1),

where S is the root mean square (RMS) signal provided at the output of the device (expressed either as a voltage or current value) and T is the source temperature. It depends on the spectral photon (a.k.a. thermal) contrast  $C_{T\lambda} (\partial \Phi_e / \partial T) / \Phi_e$ , where  $\Phi_e$  is the spectral photon incidence; also on detector responsivity and charge losses in the pixel sensor readout chain.

$$C = \frac{\partial S / \partial T}{S} \tag{1.1}$$

The MWIR spectral band is the region where thermal contrast is higher, and provides better contrast at room temperature than LWIR [17]. Even though most terrestrial objects radiate more heat in the latter region, this radiation is usually less sensitive to temperature changes.

Signal-to-Noise Ratio (SNR): In electronics, the minimum level below which a meaningful signal becomes masked and unrecoverable is usually delimited by noise or random electrical fluctuations. Considering this threshold value, the SNR provides a useful FOM in order to measure the transmission quality of a given signal of interest, defined as the ratio between the average power of signal and noise:

$$SNR = \frac{P_s}{P_n} \tag{1.2}$$